# Let the MC68701 Program Itself

Arnold J. Morales and David Ruhberg

Motorola Inc.

3501 Ed Bluestein Blvd.

Austin, TX 78721

The Motorola MC68701 is an enhanced version of the MC6801 microprocessor. One of its chief features is the ability to program itself. The processing unit controls all movement of data into an on-chip EPROM (erasable programmable read-only memory). It controls programming power ( $V_{pp}$ ) to the EPROM during programming, requiring only a few external devices to accomplish this.

On-chip resources of the MC68701 include a 2K-byte EPROM, a three-function timer, a serial-communication interface, up to 29 parallel I/O (input/output) lines, 128 bytes of RAM (random-access read/write memory), and an oscillator. These items provide a great deal of power and flexibility in a small package that's easy to use and design with.

In this article, we will explore how the MC68701 programs itself. We'll also discuss a fully tested MC68701 programmer, including software and a hardware design.

### On-Chip EPROM

A dual-purpose MC68701 pin,  $\overline{\text{RESET}}/V_{pp}$ , is used both to reset the processor and to power the EPROM. This pin is normally +5 volts (V) during nonprogramming operation. It must be raised to  $V_{pp}$  ( $21\text{ V} \pm 1\text{ V}$ ) during programming of the EPROM. However, the processor will operate normally with  $V_{pp}$  applied at all times.

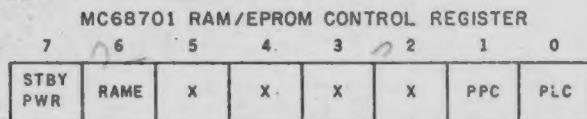

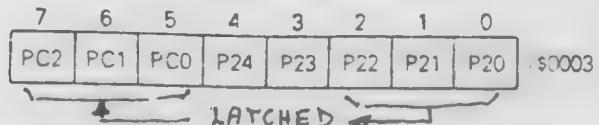

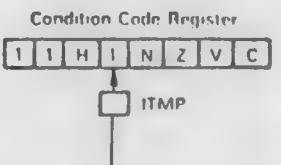

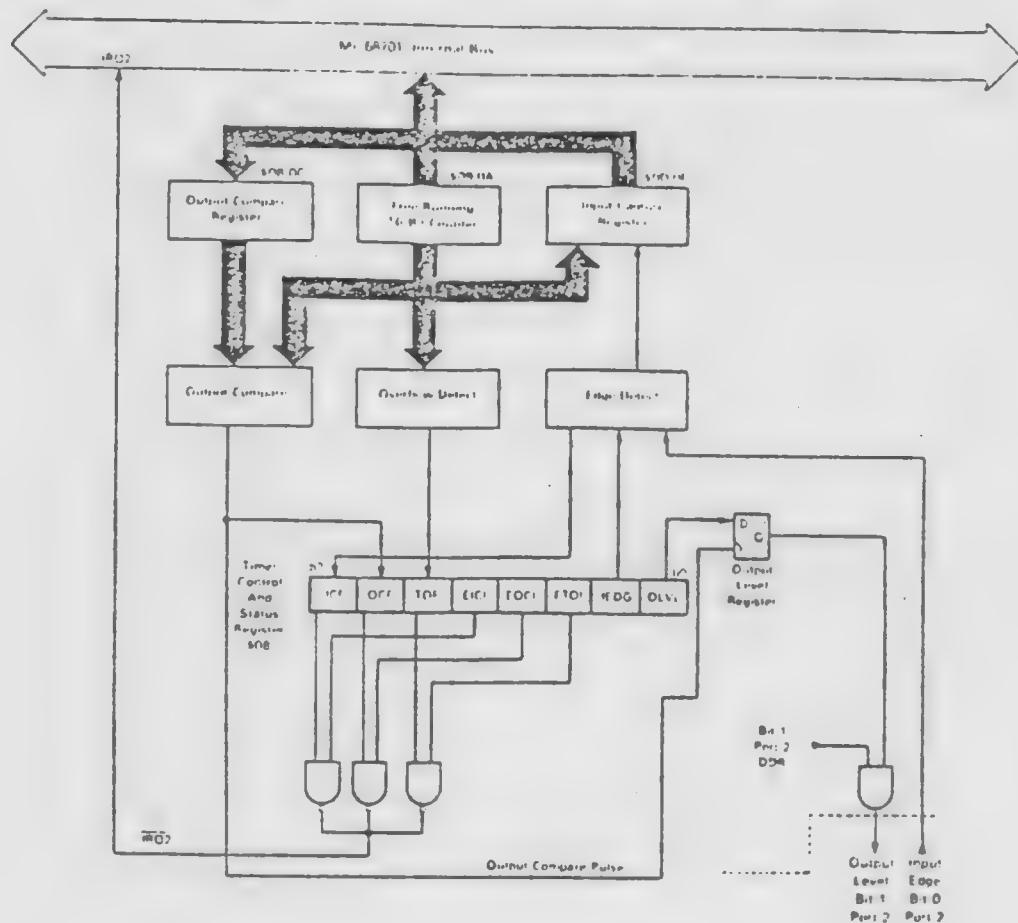

The MC68701 EPROM is controlled by two bits in the RAM/EPROM control register (see figure 1). Bit 0 of the register is called the programming latch control (PLC) and is used to control an address latch used during programming of the EPROM. Bit 1 of the register is called

Figure 1: The RAM/EPROM control register. See the text for details of its operation.

the programming power control (PPC) and is used to control  $V_{pp}$  to the EPROM during programming.

When PLC is set, the latch is transparent. When PLC is clear, the address latch is enabled and latches each EPROM address asserted by the processor. PLC should be set during normal nonprogramming processor operation; it should be cleared only to program the EPROM. This bit is set at  $\overline{\text{RESET}}$  and can be cleared only in Mode 0 (more about modes later).

When PPC is set,  $V_{pp}$  is not applied to the EPROM; when PPC is clear,  $V_{pp}$  is applied to the EPROM. PPC should be set during normal nonprogramming operation; it should be cleared only to program the EPROM. This bit is set at  $\overline{\text{RESET}}$  and whenever the PLC bit is set, and can be cleared only in Mode 0 with the PLC bit clear.

The MC68701 is programmed in Mode 0 only. In this mode, all the interrupt vectors and reset vectors are in the locations BFF0 to BFFF hexadecimal, and the on-chip EPROM is at locations F800 to FFFF hexadecimal. The

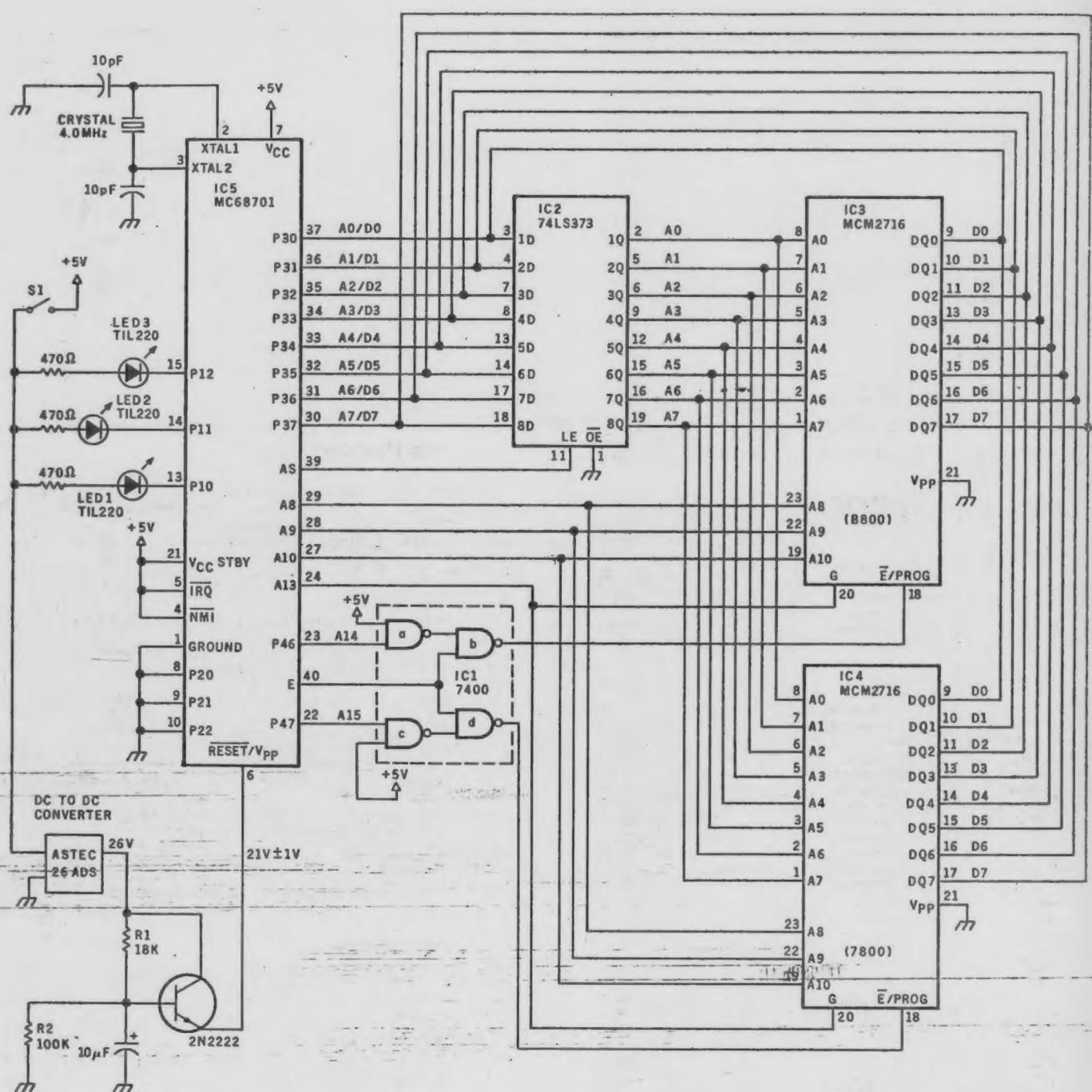

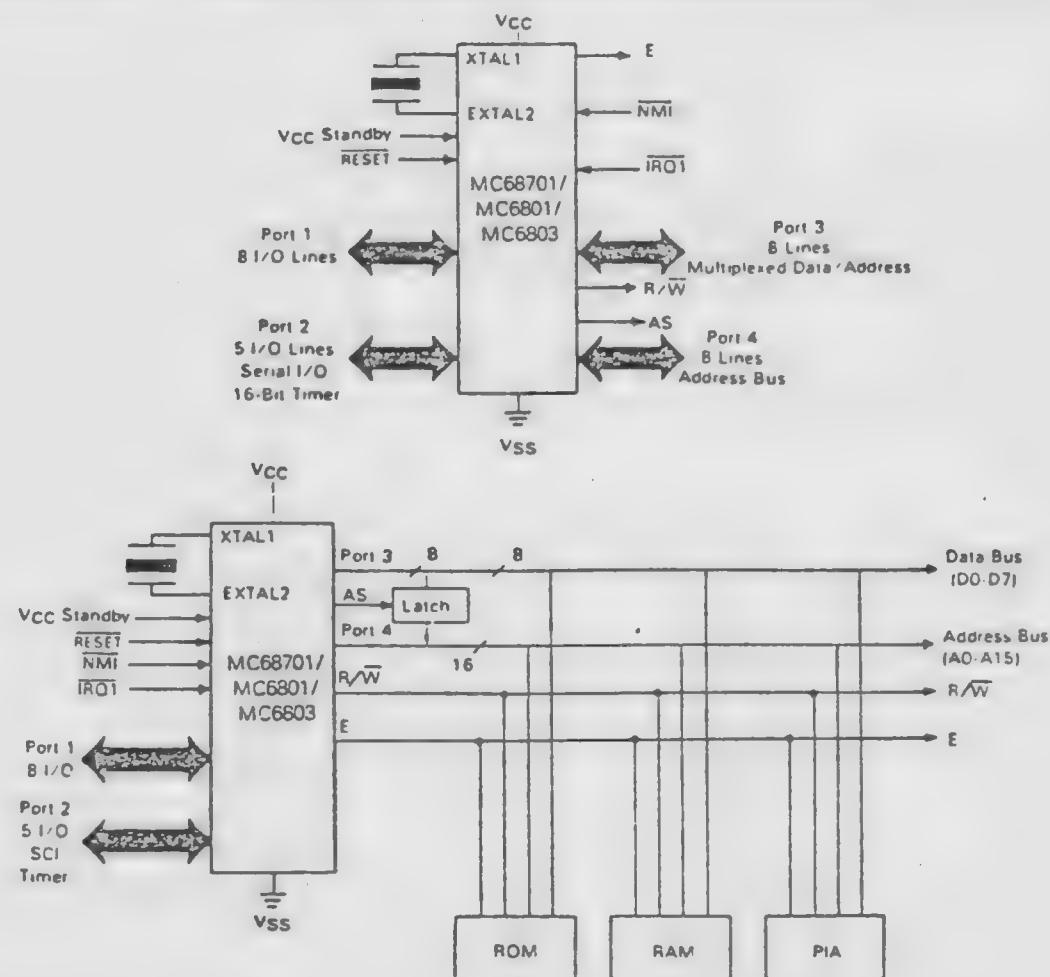

Figure 2: Programmer for the MC68701. The simplicity of this inexpensive circuit means easy construction and use. In combination with the software provided in listing 1, LEDs in the programmer can indicate that the EPROM is initially erased and that the newly stored data pass or fail a verification test.

reset vectors should direct the processor to what is essentially a bootstrap-loading program that will fetch data sequentially from memory or a peripheral controller and "burn" each byte into the EPROM. Once  $V_{pp}$  is applied to the RESET/V<sub>pp</sub> pin, each data byte is programmed into the onboard EPROM as follows:

1. Clear the PLC bit and set the PPC bit. This enables the EPROM address latch and inhibits  $V_{pp}$  to the EPROM.

2. Write data to the EPROM location to be programmed. Both the data and address will be captured by internal latches.

3. Clear the PPC bit for 50 milliseconds (ms). This controls programming power to the EPROM, allowing the data byte to be burned in.

These steps are repeated until all bytes have been programmed.

#### An MC68701 Programmer

Fully assembled and tested modules designed to program the MC68701 are available through Motorola distributors. Some users, however, may require custom programming boards designed to meet specific needs.

JOHN STARKWEATHER'S

# NEVADA PILOT

**\$149.95**

DISKETTE AND MANUAL

Vector and many other microcomputers. Needs 32K RAM, one disk drive and CRT or video display and keyboard.

- PILOT for Programmed, Inquiry, Learning Or Teaching.

- An excellent interactive language for education and office automation.

- Perfect companion for **BASIC**, **COBOL** and **PASCAL** to solve training and documentation problems.

- John Starkweather, Ph.D., creator of PILOT, wrote this version to meet all PILOT-73 standards and added many new features.

- New features include full screen text editor, commands to drive optional equipment such as VTR's & voice response units.

- Currently used in many college and progressive high schools.

- Use for interactive applications—data entry, programmed instruction and testing.

For all CP/M systems. Works with Apple (softcard needed), Osborne 1, TRS-80, North Star, Superbrain, Micropolis, one

# NEVADA EDIT

**\$119.95**

DISKETTE AND MANUAL

For all CP/M-based systems. Requires 32K RAM, one disk drive and CRT or video display and keyboard.

- A character oriented full screen video display text editor designed specifically for program preparation of **COBOL**, **FORTRAN**, **BASIC** and similar programs.

- Features include single key commands for cursor control, scrolling, block moves, search and replace, tab setting and multiple file insertions.

# NEVADA COBOL

**\$199.95**

DISKETTE AND MANUAL

For all CP/M or MP/M operating systems. Requires 32K RAM and one disk drive.

- Edition II of Nevada COBOL is based on ANSI-74 Standards.

- With 48K RAM, you can compile and execute up to 4000 statements.

- COPY statement for library handling.

- CALL...USING...CANCEL

- PERFORM...THRU...TIMES...UNTIL...paragraph or section names.

- IF...NEXT SENTENCE...ELSE...NEXT SENTENCE AND/OR <=> NOT.

- GO TO...DEPENDING ON...

- Interactive ACCEPT/DISPLAY...

- RELATIVE (random) access files

- Sequential files both fixed and variable length.

- INSPECT...TALLYING...REPLACING.

**ELLIS COMPUTING**

SOFTWARE TECHNOLOGY

600 41st Avenue, Dept. B

San Francisco, CA 94121

U.S.A.

CP/M, MP/M, TRS-80 and SoftCard system are registered TM's of Digital Research, Tandy Corporation and Microsoft respectively. Osborne 1 is a trademark of Osborne Computer Corporation.

COD's WELCOME

**(415) 751-1522**

The programmer described in this article (see figure 2) is designed for simplicity, low cost, and ease of use. The hardware and associated software verify that an inserted MC68701 is initially fully erased, do the programming, and verify the "entered" code. The user only applies power and monitors three light-emitting diodes (LEDs) that indicate EPROM status. The programmer enters the entire 2K-byte content of EPROM IC4 into the MC68701 EPROM. The system can be modified to, for instance, provide more detailed failure information or to program only a portion of the EPROM.

## Using the Programmer

The user needs no knowledge of MC68701 operation and very little knowledge of electronics in order to use the programmer. Four steps are required:

1. Insert the EPROM containing the code to be programmed into the MC68701 into the socket at IC4.

2. Insert the MC68701 into the socket.

3. Apply power.

4. Monitor LEDs.

Within a few seconds after power is applied, LED 1 should light, indicating that the MC68701 EPROM is fully erased. Approximately 105 seconds after power is applied, LED 2 should light, indicating that the EPROM has been programmed and its contents verified. At this time, power can be removed from the system, and another MC68701 can be programmed.

LED 3 will light to indicate either a not fully erased MC68701 EPROM when power is initially applied, or failure to verify after attempted programming. If LED 3 lights and LED 1 is not lit, the MC68701 was not fully erased when inserted into the board. If this occurs, no attempt is made to program the EPROM. If LED 3 lights while LED 1 is lit, the EPROM's contents did not verify after attempted programming.

The LEDs should be color-coded to give readily recognized *pass* and *fail* indication. A good color scheme is amber for LED 1 (erased), green for LED 2 (pass), and red for LED 3 (fail). Zero insertion force sockets should be used for the MC68701 and EPROM.

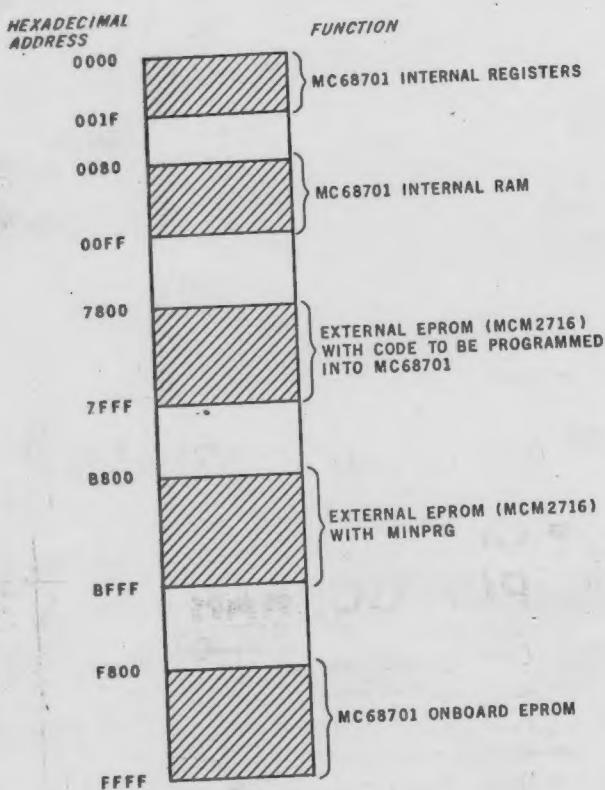

## Memory Map

The memory map, consisting of five special address spaces, is shown in figure 3. Four of the address spaces are fixed by the MC68701 during programming and cannot be relocated. These consist of an internal-register area (0000 to 001F hexadecimal), internal RAM (0080 to 00FF hexadecimal), external interrupt vectors (BFF0 to BFFF hexadecimal), and internal EPROM (F800 to FFFF hexadecimal).

A fifth address space is used for an MCM2716 that contains the code to be entered into the MC68701 on-chip EPROM. This MCM2716 has been arbitrarily placed at locations 7800 to 7FFF hexadecimal and can be relocated for custom programmer design.

Figure 3: Memory map of the MC68701 address space.

For ease of decoding, an MCM2716 containing MINPRG, the programmer bootstrap program, is based at location B800 hexadecimal. The system RESET vectors are located at the top of the EPROM and decode at locations BFFE to BFFF hexadecimal.

### Circuit Description

The MC68701 programmer consists of two MCM2716 EPROMs, a 74LS373 transparent latch, a 74LS00 NAND gate package, an MC68701 socket, and associated "glue," as shown in figure 2.

A 4-megahertz (MHz) crystal is used to yield 1-MHz operation. This clock frequency can be increased to accommodate higher-speed MC68701s, but changes in the operating frequency require changes in the MINPRG bootstrap software to ensure 50 ms programming time for each byte entered into the EPROM, or to minimize programming time.

This delay is governed by the value of WAIT in MINPRG and is indirectly related to the clock frequency. An increase in the clock frequency requires a proportional increase in the value of WAIT; a decrease of the clock frequency allows a proportional decrease in the value of WAIT.

The MC68701 can also be driven by an external transistor-transistor logic (TTL) clock at pin 3, with pin 2 grounded. If this clock option is used, the capacitors tied to pins 2 and 3, used to ensure stable crystal operation, are not required.

Pins 8, 9, and 10 are tied to ground to place the MC68701 into Mode 0 (programming mode) at RESET. IRQ (interrupt request) and NMI (nonmaskable interrupt) are tied high to eliminate external interrupts.

Three LEDs are tied to I/O pins 13, 14, and 15. They are used to indicate the state of the MC68701 EPROM during programming operations. High-current drivers force the pins low to light the LEDs.

The  $\overline{\text{RESET}}/V_{pp}$  pin is driven by a transistor to assure adequate power to the pin during programming. The base of this transistor is controlled by an RC (resistor-capacitor) network that provides adequate delay between

Text continued on page 394

Listing 1 is on pages 388-392

**THE LAST ONE™**

THE PROGRAM THAT WRITES PROGRAMS

**AVAILABLE FOR**

|                    |               |

|--------------------|---------------|

| TRS - 80 MLD II    | CP/M          |

| Apple II Plus      | Sharp PC 3201 |

| North Star Vantage |               |

Still Only \$600.00

Dealer Inquiries Invited

Send to **KROWN COMPUTING**

1282 Conference Dr., P.O. 66763

Scotts Valley, CA 95066

(408) 335-3133

Circle 225 on Inquiry card.

**WS IMPERIAL MICRO SUPPLY LTD.**

**Scotch® DISKETTES**

**DISKS SCOTCH 3M**

5 1/4" ..... \$2.30 each

Reinforced Hubs, Any Quantity

Save more on 100 or more boxes \$2.25 ea.

**MEMORY**

RAM

|            |           |

|------------|-----------|

| 4116-200NS | 8/16      |

| 4164-200NS | \$10 each |

**EPROMS**

|           |             |

|-----------|-------------|

| 2716 (5V) | \$5.50 each |

|-----------|-------------|

**X-TALS MHZ**

|     |          |        |          |       |

|-----|----------|--------|----------|-------|

| 1.0 | 3.579545 | 5.0680 | 10.0     | 18.0  |

| 2.0 | 4.0      | 5.7143 | 14.31818 | 20.00 |

| 3.0 | 5.0      | 8.0    | 16.0     |       |

**WS IMPERIAL MICRO SUPPLY LTD.**

P.O. BOX 833, DEPT. M, PONTIAC, MI 48056

Please add 12.00 Shipping — Michigan add 4% Tax

Circle 199 on Inquiry card.

**LARGE DISK CP/M USERS**

TIRE'D OF SEARCHING DIRECTORY LISTINGS FOR YOUR FILES???

ANNOUNCING the CPUTIL package:

- Allows system files to be logically moved to the current user file upon logon. This means that multiple copies of system files are not needed.

- Removes all system files from directory listings unless desired by the user.

- Restores all system files to file 0 upon logoff.

- Allows user files to be referred to by a user-defined name or the file number.

- Allows a directory listing of any user file from any other user file.

**INTRODUCTORY PRICE**

\$49.95

including manuals

Texas res. add 6% sales tax

**EARTH SCIENCE ASSOC.**

10218 Cantertrot

Humble, Tx. 77338

713-446-1555

**SATISFACTION GUARANTEED**

Circle 157 on Inquiry card.

**Listing 1: MINPRG** is the software that allows the MC68701 to program itself.

```

00001      *

00002      *

00003      *          OPT      Z01,LLEM=80

00004      *

00005      *

00006      *          THIS PROGRAM WILL CHECK, PROGRAM AND VERIFY

00007      *          THE MC68701'S EPROM

00008      *

00009      *

00010      *          E Q U A T E S

00011      0000  A P1DDR  EQU  $00      PORT 1 DATA DIR. REGISTER

00012      0002  A P1DR   EQU  $02      PORT 1 DATA REGISTER

00013      0008  A TCSR   EQU  $08      TIMER CONTROL/STAT REGISTER

00014      0009  A TIMER   EQU  $09      COUNTER REGISTER

00015      000B  A OUTCMP  EQU  $0B      OUTPUT COMPARE REGISTER

00016      0014  A EPMCNT  EQU  $14      RAM/EROM CONTROL REGISTER

00017      *

00018      *          L O C A L   V A R I A B L E S

00019      *

00020A 0080      ORG  $80

00021A 0080      0002  A IMBEG  RMB  2      START OF MEMORY BLOCK

00022A 0082      0002  A IMEND  RMB  2      LAST BYTE OF MEMORY BLOCK

00023A 0084      0002  A PNTR   RMB  2      FIRST BYTE OF EPROM TO BE PGM'D

00024A 0086      0002  A WAIT   RMB  2      COUNTER VALUE

00025      *

00026A B850      ORG  SB850

00027A B850 8E 00FF  A START LDS  #$FF      INITIALIZE STACK

00028A B853 86 07  A LDAA  #$07      INIT. PORT 1

00029A B855 97 00  A STAA  P1DDR

00030A B857 97 02  A STAA  P1DR      DATA REGISTER (ALL LED'S OFF)

00031      **

00032A B859 CE F800  A LDX   #SF800      CHECK IF EPROM ERASED

00033A B85C DF 84  A STX   PNTR      INIT. PNTR WHILE CONVENIENT

00034A B85E C6 00  A LDAB  #$00      GET READY FOR CMPR.

00035A B860 A6 00  A ERASE LDAA  0,X      LOAD EPROM CONTENTS

00036A B862 11      CBA   -

00037A B863 26 29 B88E      RNE   ERROR1      COMPARE TO ZERO

00038A B865 8C FFFF  A CPX   #$FFFF      BRANCH IF NOT ZERO

00039A B868 27 03 B86D      BEQ   NEXT      CHECK IF DONE

00040A B86A 08      INX   -

00041A B86B 20 F3 B860      BRA   ERASE      IF SO BRANCH

00042      **

00043A B86D 86 06  A NEXT LDAA  #$06      GO AGAIN

00044A B86F 97 02  A STAA  P1DR      TURN ON ERASED LED

00045      **

00046      *          WAIT FOR VPP TO REACH 21V (3.5 SEC.)

00047      *

00048A B871 DF 86  A STX   WAIT

00049A B873 CE 0046  A LDX   #$0046      GET READY FOR 70 TIMES THRU LOOP

00050A B876 09      STALL1 DEX   -

00051A B877 CC C350  A LDD   #SC350      INIT. 50MS LOOP

00052A B87A D3 09  A ADDD  TIMER      BUMP CURRENT VALUE

00053A B87C 7F 0008  A CLR   TCSR      CLEAR OCF

00054A B87F DD 0B  A STD   OUTCMP      SET OUTPUT COMPARE

00055A B881 86 40  A LDAA  #$40      NOW WAIT FOR OCF

00056A B883 95 08  A STALL2 BITA  TCSR

00057A B885 27 FC B883      BEQ   STALL2      NOT YET

00058A B887 8C 0000  A CPX   #$0000      70 TIMES YET?

```

*Listing 1 continued on page 390*

*Listing 1 continued:*

|        |      |    |      |      |        |                                        |         |                           |

|--------|------|----|------|------|--------|----------------------------------------|---------|---------------------------|

| 00059A | B88A | 26 | EA   | B876 | BNB    | STALL1                                 | NOPE    |                           |

| 00060A | B88C | 20 | 06   | B894 | BRA    | PGINT                                  |         |                           |

| 00061  |      |    |      |      | ***    |                                        |         |                           |

| 00062A | B88E | 86 | 83   | A    | ERROR1 | LDAA                                   | #\$83   | LIGHT ERROR LED ONLY      |

| 00063A | B890 | 97 | 02   | A    |        | STAA                                   | P1DR    |                           |

| 00064A | B892 | 20 | 5D   | B8F1 |        | BRA                                    | SELF    |                           |

| 00065  |      |    |      |      | ***    |                                        |         |                           |

| 00066A | B894 | CE | 7800 | A    | PGINT  | LDX                                    | #\$7800 | INIT. IMBEG               |

| 00067A | B897 | DF | 80   | A    |        | STX                                    | IMBEG   |                           |

| 00068A | B899 | CE | 7FFF | A    |        | LDX                                    | #\$7FFF | INIT. IMEND               |

| 00069A | B89C | DF | 82   | A    |        | STX                                    | IMEND   |                           |

| 00070A | B89E | CE | C350 | A    |        | LDX                                    | #\$C350 | INIT. WAIT (4.0 MHZ)      |

| 00071A | B8A1 | DF | 86   | A    |        | STX                                    | WAIT    |                           |

| 00072  |      |    |      |      | *      |                                        |         |                           |

| 00073  |      |    |      |      | *      | THIS PART FROM 68701 DATA SHEET        |         |                           |

| 00074  |      |    |      |      | *      |                                        |         |                           |

| 00075A | B8A3 | DE | 84   | A    | EPROM  | LDX                                    | PNTR    | SAVE CALLING ARGUMENT     |

| 00076A | B8A5 | 3C |      |      |        | PSHX                                   |         | RESTORE WHEN DONE         |

| 00077A | B8A6 | DE | 80   | A    |        | LDX                                    | IMBEG   | USE STACK                 |

| 00078  |      |    |      |      | *      |                                        |         |                           |

| 00079A | B8A8 | 3C |      |      | EPRO02 | PSHX                                   |         | SAVE POINTER ON STACK     |

| 00080A | B8A9 | 86 | FE   | A    |        | LDAA                                   | #\$FE   | REMOVE VPP, SET LATCH     |

| 00081A | B8AB | 97 | 14   | A    |        | STAA                                   | EPMCNT  | PPC=1, PLC=0              |

| 00082A | B8AD | A6 | 00   | A    |        | LDAA                                   | 0,X     | MOVE DATA MEMORY-TO-LATCH |

| 00083A | B8AF | DE | 84   | A    |        | LDX                                    | PNTR    | GET WHERE TO PUT IT       |

| 00084A | B8B1 | A7 | 00   | A    |        | STAA                                   | 0,X     | STASH AND LATCH           |

| 00085A | B8B3 | 08 |      |      |        | INX                                    |         | NEXT ADDR.                |

| 00086A | B8B4 | DF | 84   | A    |        | STX                                    | PNTR    | ALL SET FOR NEXT          |

| 00087A | B8B6 | 86 | FC   | A    |        | LDAA                                   | #\$FC   | ENABLE EPROM POWER (VPP)  |

| 00088A | B8B8 | 97 | 14   | A    |        | STAA                                   | EPMCNT  | PPC=0, PLC=0              |

| 00089  |      |    |      |      | *      |                                        |         |                           |

| 00090  |      |    |      |      | *      | NOW WAIT 50 MSEC TIMEOUT USING COMPARE |         |                           |

| 00091  |      |    |      |      | *      |                                        |         |                           |

| 00092A | B8BA | DC | 86   | A    |        | LDD                                    | WAIT    | GET CYCLE COUNTER         |

| 00093A | B8BC | D3 | 09   | A    |        | ADDD                                   | TIMER   | BUMP CURRENT VALUE        |

| 00094A | B8BE | 7F | 0008 | A    |        | CLR                                    | TCSR    | CLEAR OCF                 |

| 00095A | B8C1 | DD | 0B   | A    |        | STD                                    | OUTCMP  | SET OUTPUT COMPARE        |

| 00096A | B8C3 | 86 | 40   | A    |        | LDAA                                   | #\$40   | NOW WAIT FOR OCF          |

| 00097A | B8C5 | 95 | 08   | A    | EPRO04 | BITA                                   | TCSR    |                           |

| 00098A | B8C7 | 27 | FC   | B8C5 |        | BEQ                                    | EPRO04  | NOT YET                   |

| 00099  |      |    |      |      | *      |                                        |         |                           |

| 00100A | B8C9 | 38 |      |      |        | PULX                                   |         | SET UP FOR NEXT ONE       |

| 00101A | B8CA | 08 |      |      |        | INX                                    |         | NEXT                      |

| 00102A | B8CB | 9C | 82   | A    |        | CPX                                    | IMEND   | MAYBE DONE                |

| 00103A | B8CD | 23 | D9   | B8A8 |        | BLS                                    | EPRO02  | NOT YET                   |

| 00104A | B8CF | 86 | FF   | A    |        | LDAA                                   | #\$FF   | REMOVE VPP, INHIBIT LATCH |

| 00105A | B8D1 | 97 | 14   | A    |        | STAA                                   | EPMCNT  | EPROM CAN NOW BE READ     |

| 00106A | B8D3 | 38 |      |      |        | PULX                                   |         | RESTORE PNTR              |

| 00107A | B8D4 | DF | 84   | A    |        | STX                                    | PNTR    |                           |

| 00108  |      |    |      |      | *      | *                                      |         |                           |

| 00109  |      |    |      |      | *      | START NEW CODE                         |         |                           |

| 00110  |      |    |      |      | *      |                                        |         |                           |

| 00111A | B8D6 | CE | 7800 | A    |        | LDX                                    | #\$7800 | SET UP POINTER            |

| 00112A | B8D9 | 3C |      |      | VERF2  | PSHX                                   |         | SAVE POINTER ON STACK     |

| 00113A | B8DA | A6 | 00   | A    |        | LDAA                                   | 0,X     | GET DESIRED DATA          |

| 00114A | B8DC | DE | 84   | A    |        | LDX                                    | PNTR    | GET EPROM ADDR.           |

| 00115A | B8DE | E6 | 00   | A    |        | LDAB                                   | 0,X     | GET DATA TO BE CHECKED    |

| 00116A | B8E0 | 11 |      |      |        | CRA                                    |         | CHECK IF SAME             |

*Listing 1 continued on page 392*

|                             |        |         |                             |

|-----------------------------|--------|---------|-----------------------------|

| 00117A B8E1 26 10 B8F3      | BNE    | ERROR2  | BRANCH IF ERROR (LIGHT LED) |

| 00118A B8E3 08              | INX    |         | NEXT ADDR                   |

| 00119A B8E4 DF 84 A         | STX    | PNTR    | ALL SET FOR NEXT            |

| 00120A B8E6 38              | PULX   |         | SETUP FOR NEXT ONE          |

| 00121A B8E7 08              | INX    |         | NEXT                        |

| 00122A B8E8 8C 8000 A       | CPX    | #\$8000 | MAYBE DONE                  |

| 00123A B8EB 26 EC B8D9      | BNE    | VERF2   | NOT YET                     |

| 00124                       | *      | *       |                             |

| 00125A B8ED 86 84 A         | LDAA   | #\$84   |                             |

| 00126A B8EF 97 02 A         | STAA   | P1DR    | LIGHT VERIFY LED            |

| 00127                       | *      | *       |                             |

| 00128A B8F1 20 FE B8F1      | SELF   | BRA     | SELF                        |

| 00129                       | *      | *       |                             |

| 00130A B8F3 86 82 A         | ERROR2 | LDAA    | #\$82                       |

| 00131A B8F5 97 02 A         | STAA   | P1DR    |                             |

| 00132A B8F7 20 F8 B8F1      | BRA    | SELF    |                             |

| 00133                       | *      | *       |                             |

| 00134                       | *      | *       |                             |

| 00135                       | *      |         |                             |

| 00136A BFF0                 | ORG    | \$BFF0  |                             |

| 00137A BFF0                 | FDB    | SELF    |                             |

| 00138A BFF2                 | FDB    | SELF    |                             |

| 00139A BFF4                 | FDB    | SELF    |                             |

| 00140A BFF6                 | FDB    | SELF    |                             |

| 00141A BFF8                 | FDB    | SELF    |                             |

| 00142A BFFA                 | FDB    | SELF    |                             |

| 00143A BFFC                 | FDB    | SELF    |                             |

| 00144A BFFE                 | FDB    | START   |                             |

| 00145                       | END    |         |                             |

| TOTAL ERRORS 000000--000000 |        |         |                             |

|             |                                                             |       |       |

|-------------|-------------------------------------------------------------|-------|-------|

| 0014 EPMCNT | 00016*00081                                                 | 00088 | 00105 |

| B8A3 EPROM  | 00075*                                                      |       |       |

| B8A8 EPRO02 | 00079*00103                                                 |       |       |

| B8C5 EPRO04 | 00097*00098                                                 |       |       |

| B860 ERASE  | 00035*00041                                                 |       |       |

| B88E ERROR1 | 00037 00062*                                                |       |       |

| B8F3 ERROR2 | 00117 00130*                                                |       |       |

| 0080 IMBEG  | 00021*00067 00077                                           |       |       |

| 0082 IMEND  | 00022*00069 00102                                           |       |       |

| B86D NEXT   | 00039 00043*                                                |       |       |

| 000B OUTCMP | 00015*00054 00095                                           |       |       |

| 0000 P1DDR  | 00011*00029                                                 |       |       |

| 0002 P1DR   | 00012*00030 00044 00063 00126 00131                         |       |       |

| B894 PGINT  | 00060 00066*                                                |       |       |

| 0084 PNTR   | 00023*00033 00075 00083 00086 00107 00114 00119             |       |       |

| B8F1 SELF   | 00064 00128*00128 00132 00137 00138 00139 00140 00141 00142 |       |       |

|             | 00143                                                       |       |       |

| B875 STALL1 | 00050*00059                                                 |       |       |

| B883 STALL2 | 00056*00057                                                 |       |       |

| B850 START  | 00027*00144                                                 |       |       |

| 0008 TCSR   | 00013*00053 00056 00094 00097                               |       |       |

| 0009 TIMER  | 00014*00052 00093                                           |       |       |

| B8D9 VERF2  | 00112*00123                                                 |       |       |

| 0086 WAIT   | 00024*00048 00071 00092                                     |       |       |

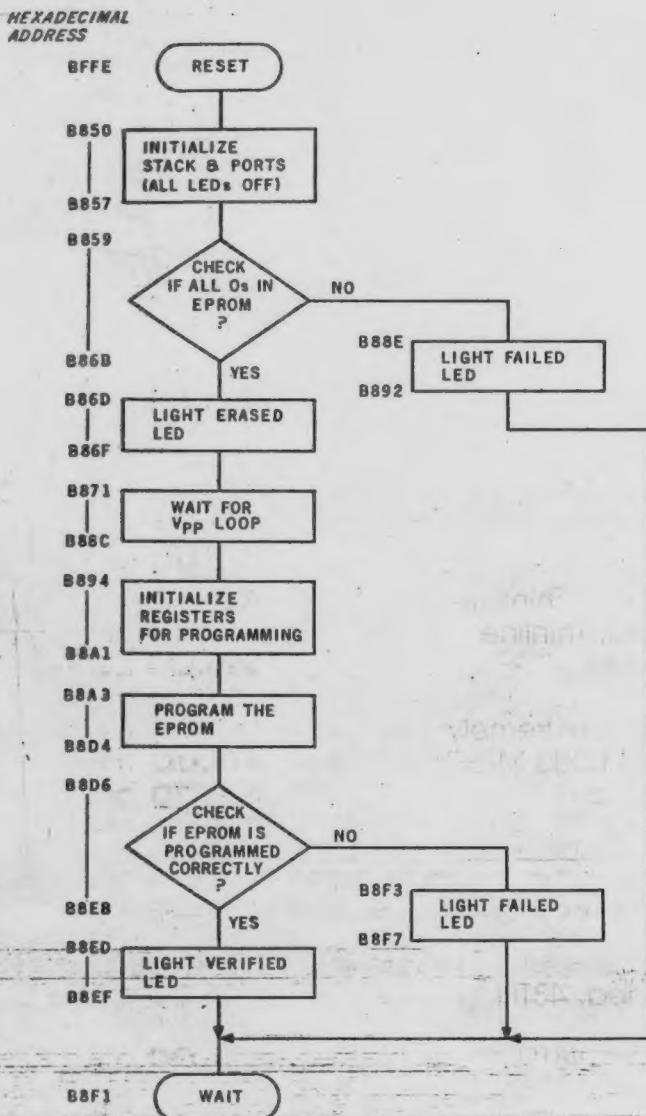

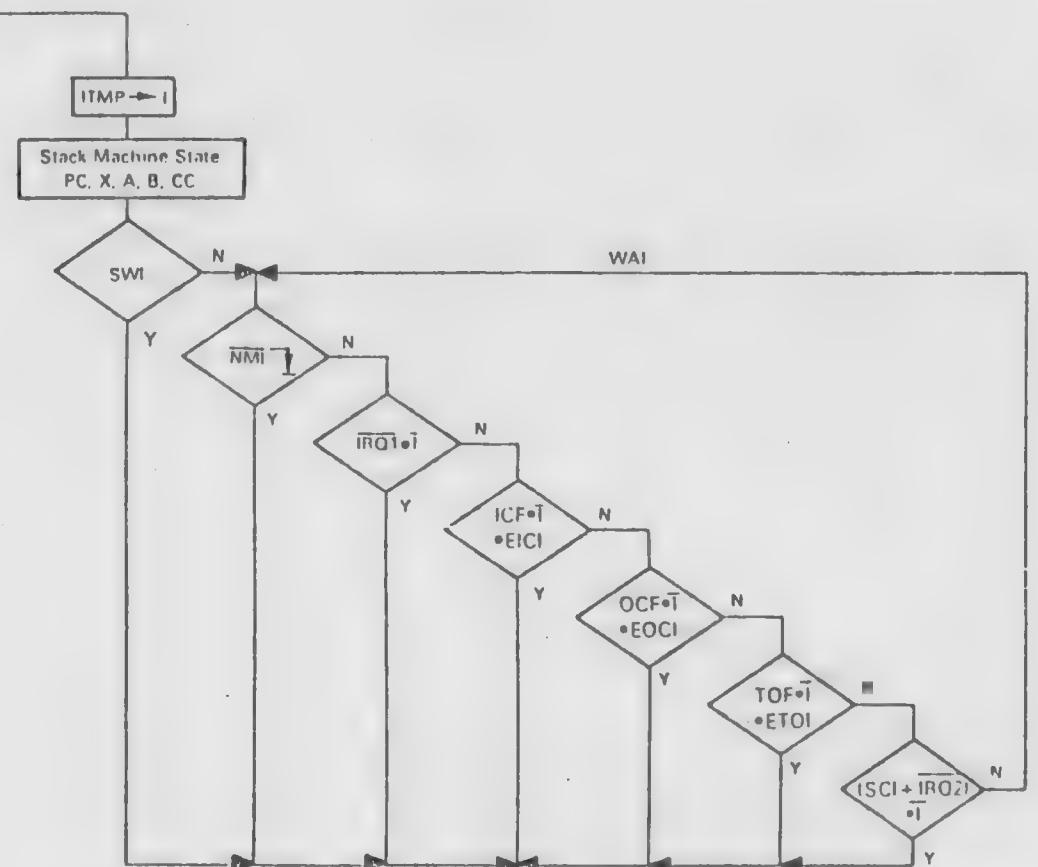

Figure 4: Flowchart of the programmer software called MINPRG. The program is shown in listing 1.

Text continued from page 386:

the application of  $V_{cc}$  and  $\overline{RESET}$ . During programming,  $21\text{ V} \pm 1\text{ V}$  ( $V_{pp}$ ) must be applied to the  $\overline{RESET}/V_{pp}$  pin. A 5- to 26-V voltage converter is used to eliminate the need for two power supplies.  $R1$  and  $R2$  form a voltage divider that provides a proper voltage level to the  $\overline{RESET}/V_{pp}$  pin.  $R2$  also serves to discharge  $C1$  during power-down.

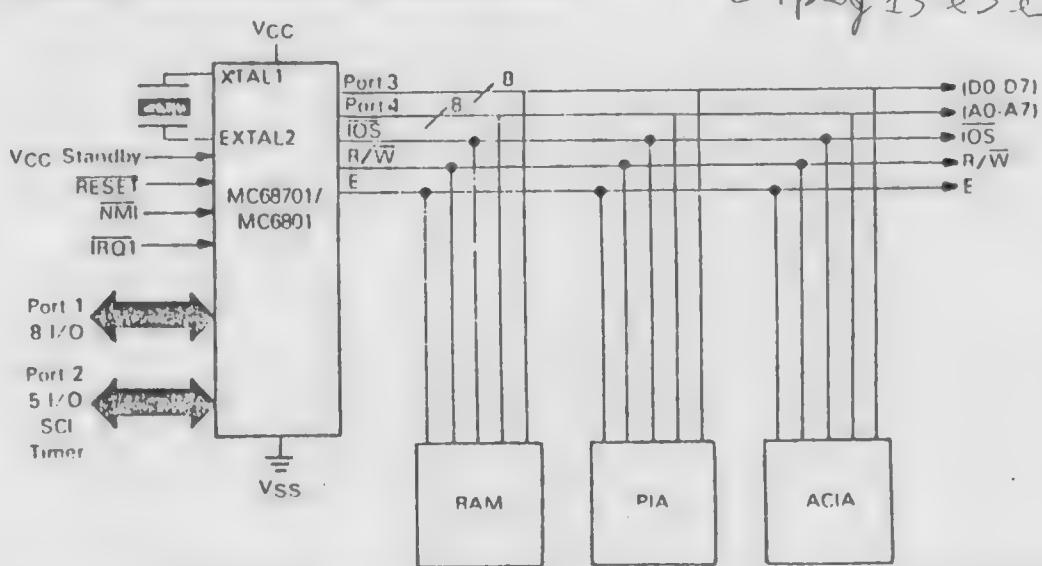

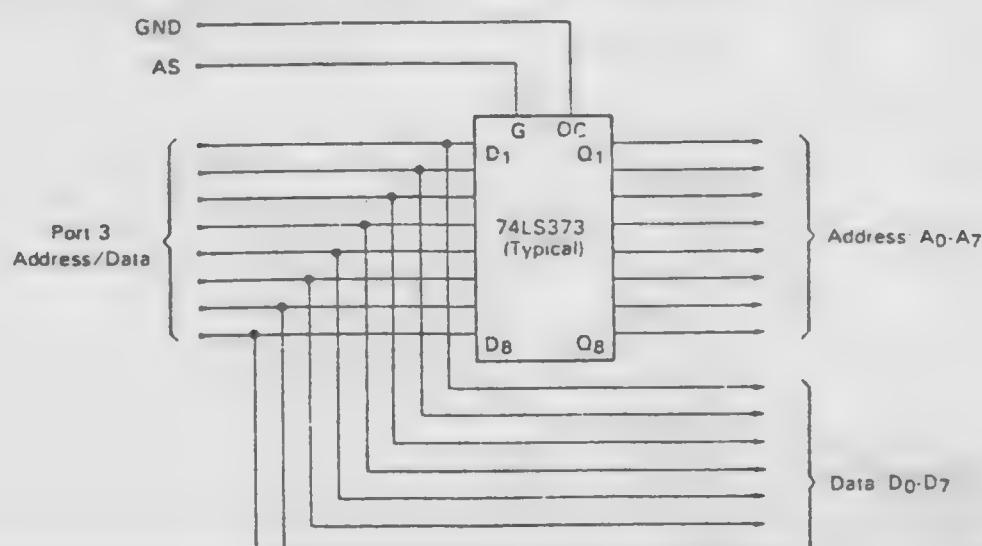

A 74LS373 transparent latch is used to demultiplex port 3, which is used both as a lower address port (signals  $A_0$  through  $A_7$ ) and as a data port. An address strobe (AS) from the MC68701 is tied to latch enable (LE) of the 74LS373 to latch the lower-order address at the proper time each bus cycle. Once the lower address is latched, the port is used for data transfer.

Four NAND gates are used for address decoding of the two external EPROMs. Each EPROM is selected with high  $A_{13}$  to ensure deselection during access of MC68701 internal RAM and internal registers. EPROM IC3 drivers are enabled with low  $A_{14}$  and high  $E$ ; EPROM IC4 drivers

are enabled with low  $A_{15}$  and high  $E$ . Controlling with  $E$  ensures that drivers are in the high-impedance state during  $E$  low, eliminating driver contention on the multiplexed lower-address/data bus. Controlling the drivers with low  $A_{14}/A_{15}$  assures separation between the off-chip and on-chip EPROM address spaces. EPROM IC3, containing MINPRG, is selected at locations B800 to BFFF hexadecimal; EPROM IC4, containing the program to be entered into the MC68701 EPROM, is selected at locations 7800 to 7FFF hexadecimal. Incomplete address decoding is used for IC3 and IC4 to minimize the number of devices used in the system, allowing their selection in several address spaces. Care must be taken when writing software for the system to ensure that only one device is accessed at any time.

Note that only Motorola MCM2716 EPROMs allow an optional active high chip select (pin 20) by tying  $V_{pp}$  (pin 21) low during reads. If non-Motorola 2716 EPROMs are used,  $V_{pp}$  must be tied high and  $A_{13}$  must be inverted to the active low chip selects.

### Program Description

The programmer uses a bootstrap program, MINPRG, to control programming of the MC68701 EPROM. The program performs the following functions:

1. Initialize the MC68701.

2. Check that the EPROM is erased.

3. Program the EPROM.

4. Verify the program.

5. Stop.

MINPRG also controls three LEDs that indicate MC68701 EPROM status during programmer operation. A detailed flowchart of MINPRG is shown in figure 4; a complete listing is shown in listing 1 on page 388.

### Program Modifications and Considerations

Additions and modifications to this code can be made easily by inserting routines between the basic blocks on the flowchart. For convenience, the start and stop addresses of each block are located directly to the left of each block.

Parameters IMBEG, IMEND, PNTR, and WAIT, stored in RAM locations 80 to 87 hexadecimal, determine the size of the data block to be programmed into the MC68701, the first MC68701 EPROM location to be programmed, and the time period each byte will be burned into the EPROM. These parameters can be changed to allow programming of selected EPROM locations and to allow changes in operating frequency. These parameters, once selected, should remain constant throughout the entire program.

A modification to MINPRG that should be considered is verification of the EPROM if the EPROM is not initially erased, rather than to simply light LED 1 and wait. This change would allow verification of MC68701 EPROMs that have already been programmed and used. ■

**MOTOROLA**

**Semiconductors**

## Advance Information

### MC68701 MICROCOMPUTER UNIT (MCU)

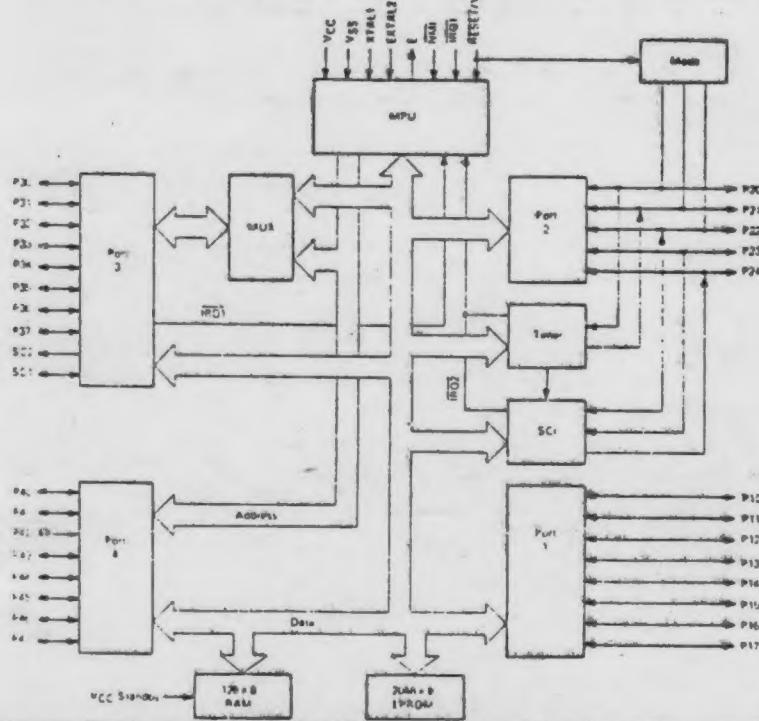

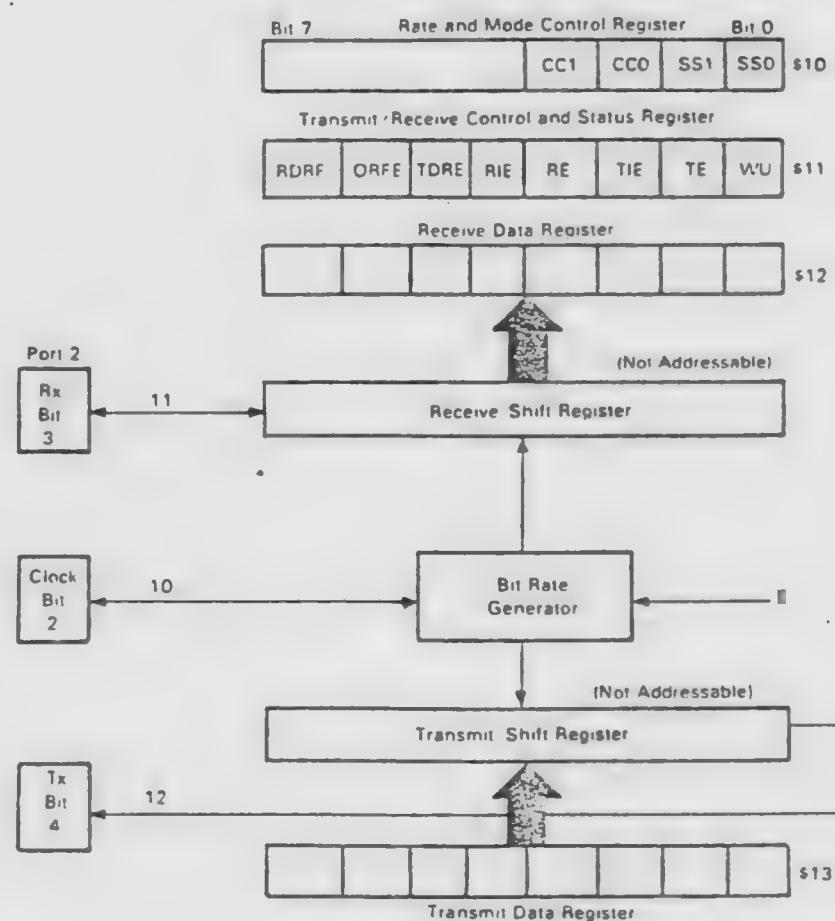

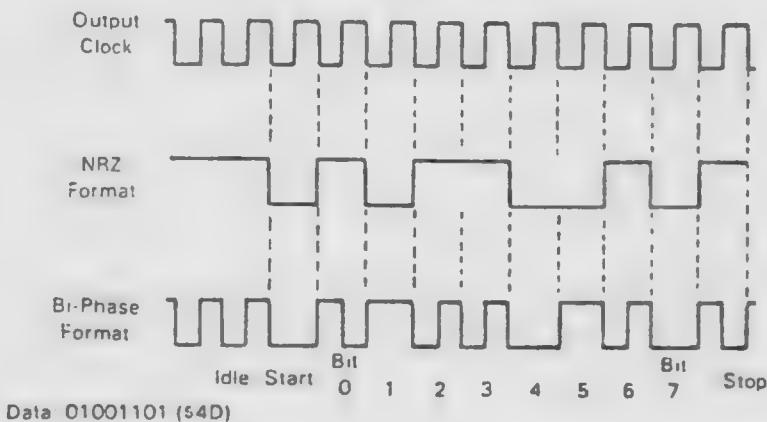

The MC68701 is an 8-bit single chip microcomputer unit (MCU) which significantly enhances the capabilities of the M6800 family of parts. It can be used in production systems to allow for easy firmware changes with minimum delay or it can be used to emulate the MC6801/03 for software development. It includes an upgraded M6800 microprocessor unit (MPU) while retaining upward source and object code compatibility. Execution times of key instructions have been improved and several new instructions have been added including an unsigned multiply. The MCU can function as a monolithic microcomputer or can be expanded to a 64K byte address space. It is TTL compatible and requires one +5 volt power supply for nonprogramming operation. An additional VPP power supply is needed for EPROM programming. On-chip resources include 2048 bytes of EPROM, 128 bytes of RAM, Serial Communications Interface (SCI), parallel I/O, and a three function Programmable Timer. A summary of MCU features includes:

- Enhanced MC6800 Instruction Set

- 8x8 Multiply Instruction

- Serial Communications Interface (SCI)

- Upward Source and Object Code Compatible with MC6800

- 16-Bit Three-Function Programmable Timer

- Single-Chip or Expandable to 64K-Byte Address Space

- Bus Compatible with M6800 Family

- 2048 Bytes of UV Erasable, User Programmable ROM

- 128 Bytes of RAM (64 Bytes Retainable on Powerdown)

- 29 Parallel I/O and Two Handshake Control Lines

- Internal Clock Generator with Divide-by-Four Output

FIGURE 2 - MC68701 MICROCOMPUTER BLOCK DIAGRAM

AD0009

THIS IS ADVANCE INFORMATION AND SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE.

**MC68701**

(1.0 MHz)

**MC68701-1**

(1.25 MHz)

### MOS

(IN-CHANNEL, SILICON-GATE,

DEPLETION LOAD)

### MICROCOMPUTER WITH EPROM

**Cramber Italia s.p.a.**

DISTRIBUZIONE ESCLUSIVA

MOTOROLA

RONDA - Via C. Colombo, 124 - Tel. 51.7.7.9

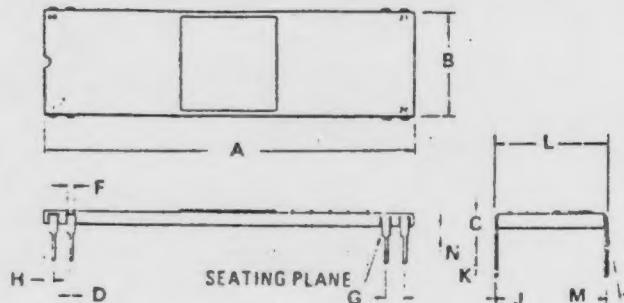

FIGURE 1 - PIN ASSIGNMENT

|           |    |                |

|-----------|----|----------------|

| VSS       | 1  | E              |

| XTAL1     | 2  | 39 SC1         |

| EXTAL2    | 3  | 38 SC2         |

| NMI       | 4  | 37 P30         |

| IRD1      | 5  | 36 P31         |

| RESET/VPP | 6  | 35 P32         |

| VCC       | 7  | 34 P33         |

| P20       | 8  | 33 P34         |

| P21       | 9  | 32 P35         |

| P22       | 10 | 31 P36         |

| P23       | 11 | 30 P37         |

| P24       | 12 | 29 P40         |

| P10       | 13 | 28 P41         |

| P11       | 14 | 27 P42         |

| P12       | 15 | 26 P43         |

| P13       | 16 | 25 P44         |

| P14       | 17 | 24 P45         |

| P15       | 18 | 23 P46         |

| P16       | 19 | 22 P47         |

| P17       | 20 | 21 VCC Standby |

©MOTOROLA INC., 1980

AD-839

## MAXIMUM RATINGS

| Rating                      | Symbol           | Value        | Unit |

|-----------------------------|------------------|--------------|------|

| Supply Voltage              | V <sub>CC</sub>  | -0.3 to +7.0 | Vdc  |

| Input Voltage               | V <sub>in</sub>  | -0.3 to +7.0 | Vdc  |

| Operating Temperature Range | T <sub>A</sub>   | 0 to 50      | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | 0 to +85     | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub> ≤ (V<sub>in</sub> or V<sub>out</sub>) ≤ V<sub>CC</sub>.

## THERMAL CHARACTERISTICS

| Characteristic                        | Symbol          | Value | Rating |

|---------------------------------------|-----------------|-------|--------|

| Thermal Resistance<br>Ceramic Package | θ <sub>JA</sub> | 50    | °C/W   |

ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5.0 V ± 5%, V<sub>SS</sub> = 0, T<sub>A</sub> = 70°C unless otherwise noted)

| Characteristic                                                                                                                                                                              | Symbol                                             | Min                                                                        | Typ                          | Max                                | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|------------------------------|------------------------------------|------|

| Input High Voltage<br>RESET<br>Other Inputs*                                                                                                                                                | V <sub>IH</sub>                                    | V <sub>SS</sub> + 4.0<br>V <sub>SS</sub> + 2.0                             | —<br>—                       | V <sub>CC</sub><br>V <sub>CC</sub> | Vdc  |

| Input Low Voltage<br>All Inputs*                                                                                                                                                            | V <sub>IL</sub>                                    | V <sub>SS</sub> - 0.3                                                      | —                            | V <sub>SS</sub> + 0.8              | Vdc  |

| Input Current<br>(V <sub>in</sub> = 0 to 2.4 Vdc)                                                                                                                                           | I <sub>in</sub>                                    | —<br>—                                                                     | —<br>—                       | 0.5<br>0.8                         | mA   |

| Input Current<br>(V <sub>in</sub> = 0 to 5.25 Vdc)                                                                                                                                          | I <sub>in</sub>                                    | —<br>—                                                                     | 1.5<br>—                     | 2.5<br>—                           | μA   |

| Input Current<br>(V <sub>in</sub> = 0 to 0.8 Vdc)<br>(V <sub>in</sub> = 4.0 Vdc to V <sub>CC</sub> )                                                                                        | I <sub>in</sub>                                    | —<br>—                                                                     | —<br>—                       | 2.0<br>8.0                         | mA   |

| Three-State (Off State) Input Current<br>(V <sub>in</sub> = 0.5 to 2.4 Vdc)                                                                                                                 | I <sub>TSI</sub>                                   | —<br>—                                                                     | 2.<br>10.0                   | 10<br>100                          | μA   |

| Output High Voltage<br>(I <sub>load</sub> = -205 μA, V <sub>CC</sub> = min)<br>(I <sub>load</sub> = -145 μA, V <sub>CC</sub> = min)<br>(I <sub>load</sub> = -100 μA, V <sub>CC</sub> = min) | V <sub>OH</sub>                                    | V <sub>SS</sub> + 2.4<br>V <sub>SS</sub> + 2.4<br>V <sub>SS</sub> + 2.4    | —<br>—<br>—                  | —<br>—<br>—                        | Vdc  |

| Output Low Voltage<br>(I <sub>load</sub> = 2.0 mA, V <sub>CC</sub> = min)                                                                                                                   | V <sub>OL</sub>                                    | —                                                                          | —                            | V <sub>SS</sub> + 0.5              | Vdc  |

| Darlington Drive Current<br>(V <sub>O</sub> = 1.5 Vdc)                                                                                                                                      | I <sub>OH</sub>                                    | 1.0                                                                        | 2.5                          | 10.0                               | mA   |

| Power Dissipation                                                                                                                                                                           | P <sub>D</sub>                                     | —                                                                          | —                            | 1200                               | mw   |

| Input Capacitance<br>(V <sub>in</sub> = 0, T <sub>A</sub> = 25°C, f <sub>0</sub> = 1.0 MHz)                                                                                                 | C <sub>in</sub>                                    | —<br>—                                                                     | —<br>—                       | 12.5<br>10.0                       | pF   |

| V <sub>CC</sub> Standby                                                                                                                                                                     | Powerdown<br>Powerup                               | V <sub>SBB</sub><br>V <sub>SB</sub>                                        | 4.0<br>4.75                  | 5.25<br>5.25                       | Vdc  |

| Standby Current                                                                                                                                                                             | I <sub>SBB</sub>                                   | —                                                                          | —                            | 6.0                                | mA   |

| Frequency of Operation<br>MC68701 External Clock<br>MC68701 Crystal<br>MC68701-1 External Clock<br>MC68701-1 Crystal                                                                        | EXTAL2<br>XTAL1, EXTAL2<br>EXTAL2<br>XTAL1, EXTAL2 | f <sub>1</sub><br>f <sub>XTAL</sub><br>f <sub>1</sub><br>f <sub>XTAL</sub> | 2.0<br>3.579<br>2.0<br>3.579 | 4.0<br>4.0<br>5.0<br>5.0           | MHz  |

| Programming Time (Per Byte)                                                                                                                                                                 | T <sub>PP</sub>                                    | 50                                                                         | —                            | —                                  | ms   |

| Programming Voltage                                                                                                                                                                         | V <sub>PP</sub>                                    | 20.0                                                                       | 21.0                         | 22.0                               | Vdc  |

| Programming Current (V <sub>RESET</sub> = V <sub>PP</sub> )                                                                                                                                 | I <sub>PP</sub>                                    | —                                                                          | —                            | 30.0                               | mA   |

\* Except Mode Programming Levels; See Figure 17.

MOTOROLA Semiconductor Products Inc.

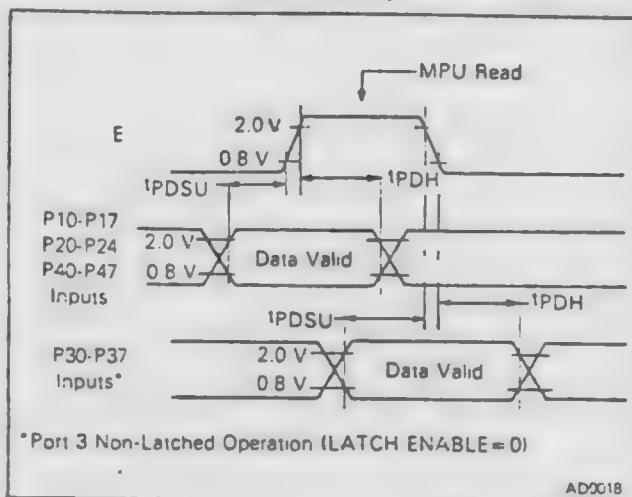

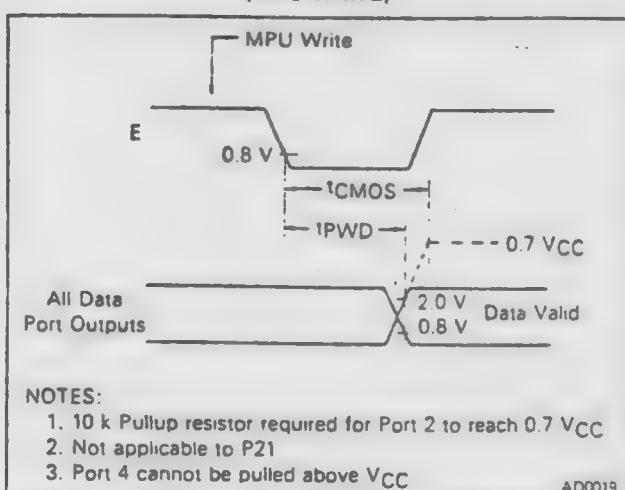

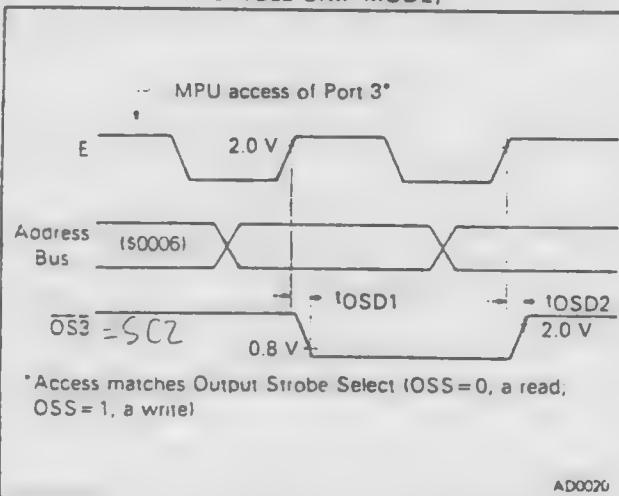

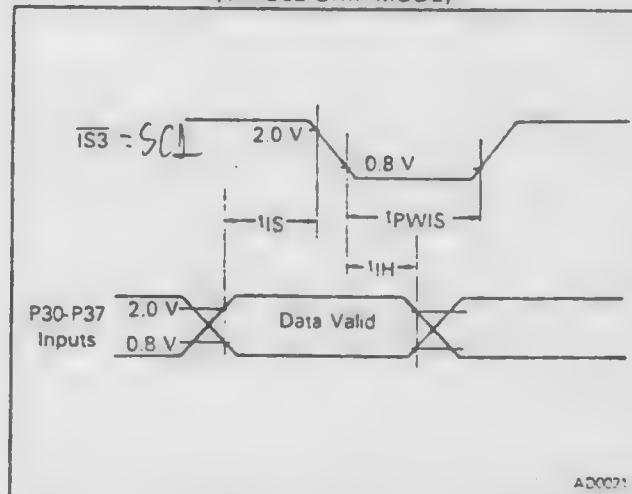

## PERIPHERAL PORT TIMING (Refer to Figures 3-6)

| Characteristics                                                                           | Symbol     | Min | Typ | Max        | Unit    |

|-------------------------------------------------------------------------------------------|------------|-----|-----|------------|---------|

| Peripheral Data Setup Time                                                                | $t_{PDSU}$ | 200 | —   | —          | ns      |

| Peripheral Data Hold Time                                                                 | $t_{PDH}$  | 200 | —   | —          | ns      |

| Delay Time, Enable Positive Transition to $\bar{OS3}$ Negative Transition                 | $t_{OSD1}$ | —   | —   | 350        | ns      |

| Delay Time, Enable Positive Transition to $\bar{OS3}$ Positive Transition                 | $t_{OSD2}$ | —   | —   | 350        | ns      |

| Delay Time, Enable Negative Transition to Peripheral Data Valid<br>Port 1<br>Port 2, 3, 4 | $t_{PWD}$  | —   | —   | 500<br>350 | ns      |

| Delay Time, Enable Negative Transition to Peripheral CMOS Data Valid                      | $t_{CMOS}$ | —   | —   | 2.0        | $\mu$ s |

| Input Strobe Pulse Width                                                                  | $t_{PWIS}$ | 200 | —   | —          | ns      |

| Input Data Hold Time                                                                      | $t_{IH}$   | 50  | —   | —          | ns      |

| Input Data Setup Time                                                                     | $t_{IS}$   | 20  | —   | —          | ns      |

FIGURE 3 — DATA SETUP AND HOLD TIMES

(MPU READ)FIGURE 4 — DATA SETUP AND HOLD TIMES

(MPU WRITE)FIGURE 5 — PORT 3 OUTPUT STROBE TIMING

(SINGLE CHIP MODE)FIGURE 6 — PORT 3 LATCH TIMING

(SINGLE CHIP MODE)

MOTOROLA Semiconductor Products Inc.

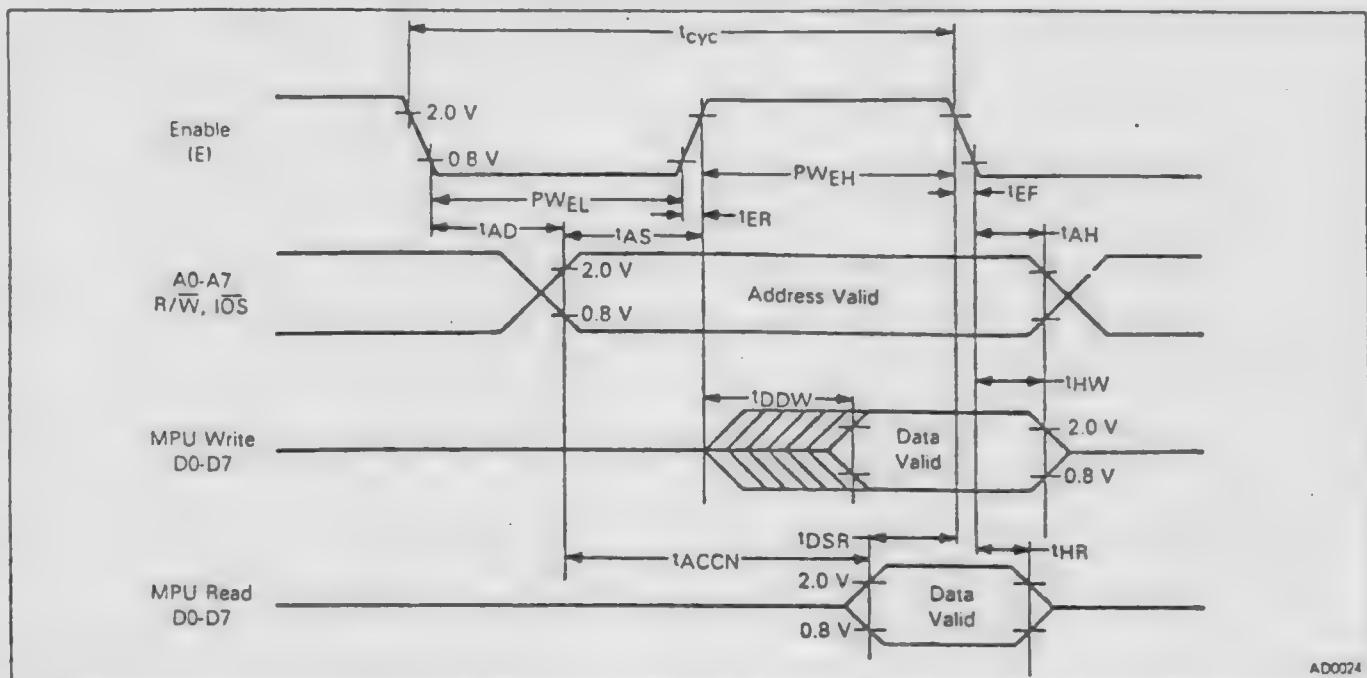

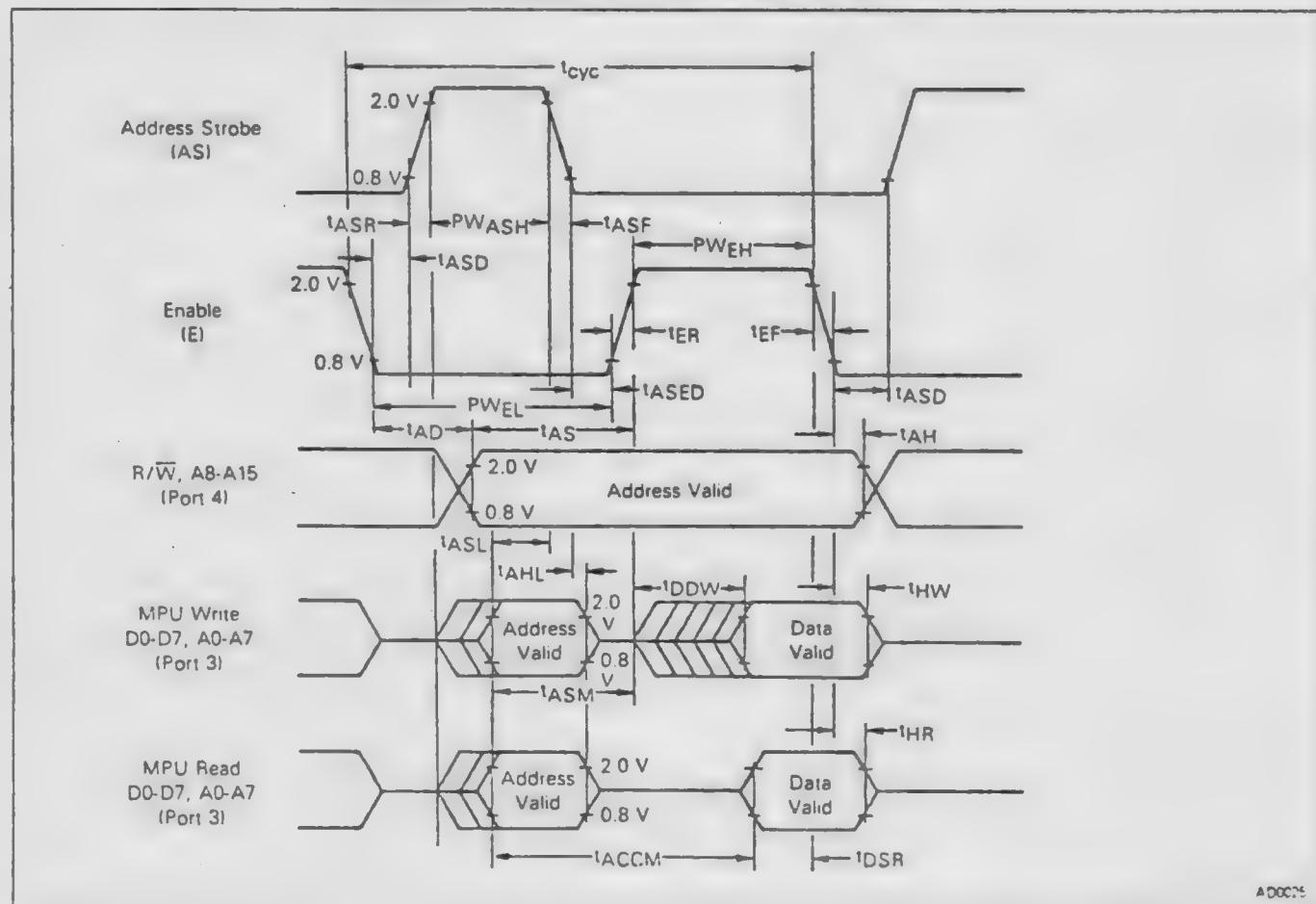

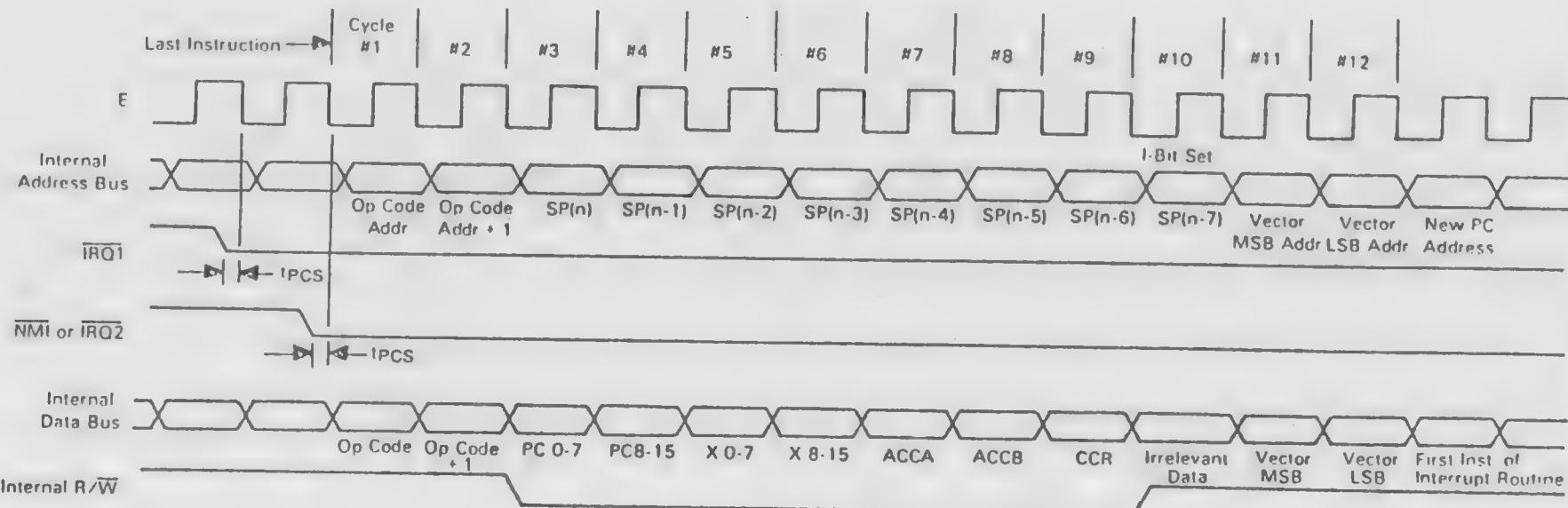

## BUS TIMING (Refer to Figures 9 and 10 and 22b)

| Characteristic                      | Symbol     | MC68701<br>( $f_0 = 1.0$ MHz) |                      |     | MC68701-1<br>( $f_0 = 1.25$ MHz) |                      |     |         |

|-------------------------------------|------------|-------------------------------|----------------------|-----|----------------------------------|----------------------|-----|---------|

|                                     |            | Min                           | Typ                  | Max | Min                              | Typ                  | Max |         |

| Cycle Time                          | $t_{cyc}$  | 1                             | —                    | 2   | 0.8                              | —                    | 2   | $\mu s$ |

| Address Strobe Pulse Width High     | $PWASH$    | 200                           | $\frac{1}{2}t_{cyc}$ | —   | 150                              | $\frac{1}{2}t_{cyc}$ | —   | ns      |

| Address Strobe Rise Time            | $t_{ASR}$  | 5                             | —                    | 30  | 5                                | —                    | 30  | ns      |

| Address Strobe Fall Time            | $t_{ASF}$  | 5                             | —                    | 30  | 5                                | —                    | 30  | ns      |

| Address Strobe Delay Time           | $t_{ASD}$  | 60                            | $\frac{1}{2}t_{cyc}$ | —   | 30                               | $\frac{1}{2}t_{cyc}$ | —   | ns      |

| Enable Rise Time                    | $t_{ER}$   | 5                             | —                    | 30  | 5                                | —                    | 30  | ns      |

| Enable Fall Time                    | $t_{EF}$   | 5                             | —                    | 30  | 5                                | —                    | 30  | ns      |

| Enable Pulse Width High Time        | $PWEH$     | 450                           | $\frac{1}{2}t_{cyc}$ | —   | 340                              | $\frac{1}{2}t_{cyc}$ | —   | ns      |

| Enable Pulse Width Low Time         | $PWEL$     | 450                           | $\frac{1}{2}t_{cyc}$ | —   | 350                              | $\frac{1}{2}t_{cyc}$ | —   | ns      |

| Address Strobe to Enable Delay Time | $t_{ASED}$ | 60                            | —                    | —   | 30                               | —                    | —   | ns      |

| Address Delay Time                  | $t_{AD}$   | —                             | —                    | 260 | —                                | —                    | 220 | ns      |

| Data Delay Write Time               | $t_{DDW}$  | —                             | —                    | 225 | —                                | —                    | 225 | ns      |

| Data Set-up Time                    | $t_{DSR}$  | 80                            | —                    | —   | 70                               | —                    | —   | ns      |

| Data Hold Time                      |            |                               |                      |     |                                  |                      |     |         |

| Read                                | $t_{HR}$   | 10                            | —                    | —   | 10                               | —                    | —   | ns      |

| Write                               | $t_{HW}$   | 20                            | —                    | —   | 20                               | —                    | —   | ns      |

| Address Setup Time for Latch        | $t_{ASL}$  | 20                            | —                    | —   | 20                               | —                    | —   | ns      |

| Address Hold Time for Latch         | $t_{AHL}$  | 20                            | —                    | —   | 20                               | —                    | —   | ns      |

| Address Hold Time                   | $t_{AH}$   | 20                            | —                    | —   | 20                               | —                    | —   | ns      |

| Address, R/W Set-up Time Before E   | $t_{AS}$   | 200                           | —                    | —   | 140                              | —                    | —   | ns      |

| A0-A7 Set-up Time Before E          | $t_{ASM}$  | 190                           | —                    | —   | 130                              | —                    | —   | ns      |

| Peripheral Read Access Time:        |            |                               |                      |     |                                  |                      |     |         |

| Non-Multiplexed Bus                 | $t_{ACCN}$ | —                             | —                    | 570 | —                                | —                    | 410 | ns      |

| Multiplexed Bus                     | $t_{ACCM}$ | —                             | —                    | 560 | —                                | —                    | 400 | ns      |

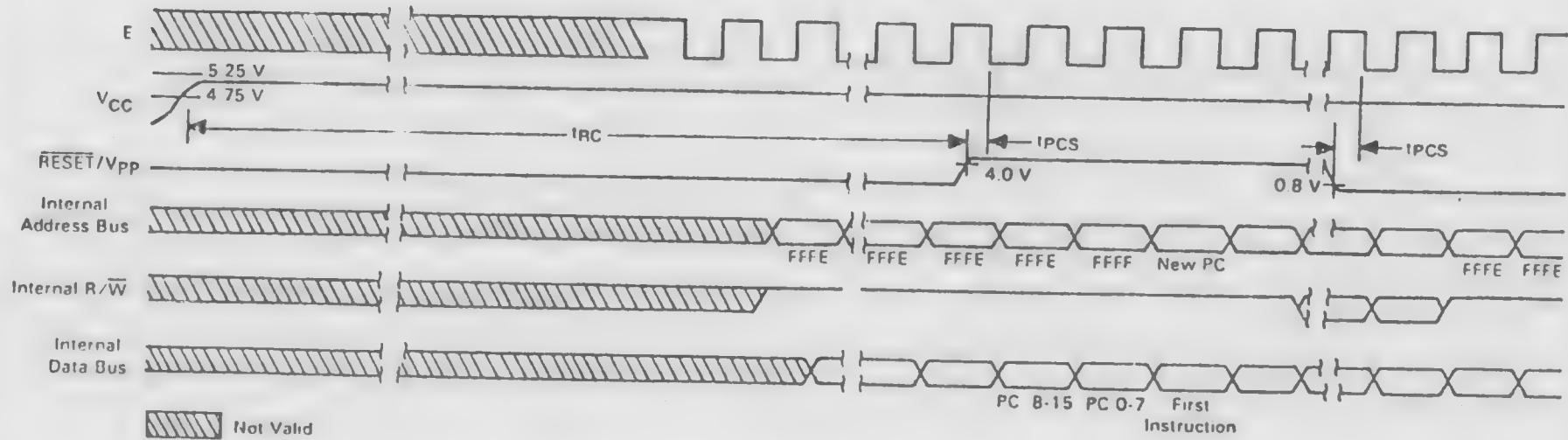

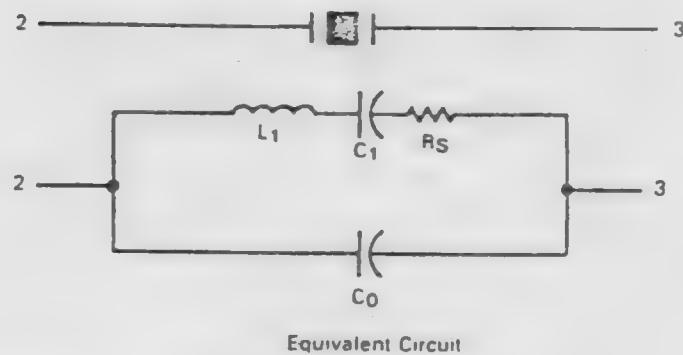

| Oscillator Stabilization Time       | $t_{RC}$   | 100                           | —                    | —   | 100                              | —                    | —   | ms      |

| Processor Control Setup Time        | $t_{PCS}$  | 200                           | —                    | —   | 200                              | —                    | —   | ns      |

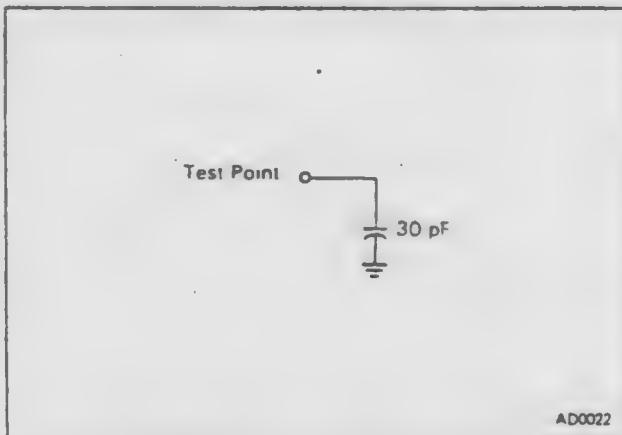

FIGURE 7 — CMOS LOAD

AD0022

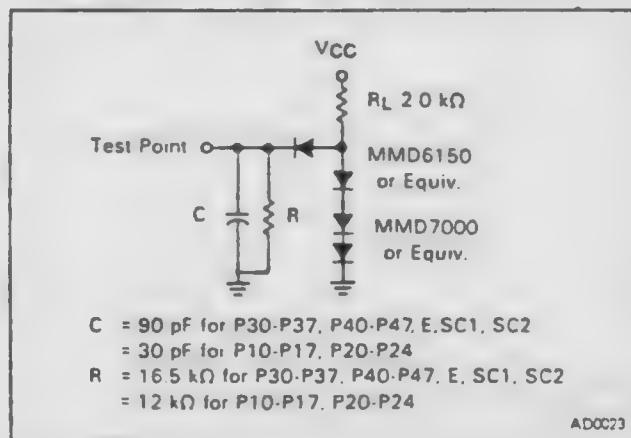

FIGURE 8 — TIMING TEST LOAD PORTS 1, 2, 3, 4

AD0023

MOTOROLA Semiconductor Products Inc.

FIGURE 9 — EXPANDED NON-MULTIPLEXED BUS TIMING

AD0024

FIGURE 10 — EXPANDED MULTIPLEXED BUS TIMING

AD0025

MOTOROLA Semiconductor Products Inc.

## INTRODUCTION

The MC68701 is an 8-bit monolithic microcomputer which can be configured to function in a wide variety of applications. The facility which provides this extraordinary flexibility is its ability to be hardware programmed into eight different operating modes. The operating mode controls the configuration of 18 of the MCU's 40 pins, available on-chip resources, memory map, location (internal or external) of interrupt vectors, and type of external bus. The configuration of the remaining 22 pins is not dependent on the operating mode.

Twenty-nine pins are organized as three 8-bit ports and one 5-bit port. Each port consists of at least a Data Register and a write-only Data Direction Register. The Data Direction Register is used to define whether corresponding bits in the Data Register are configured as an input (clear) or output (set).

The term "port," by itself, refers to all of its associated hardware. When the port is used as a "data port" or "I/O port," it is controlled by its Data Direction Register and the programmer has direct access to its pins using the port's Data Register. Port pins are labeled as  $P_{ij}$  where  $i$  identifies one of four ports and  $j$  indicates the particular bit.

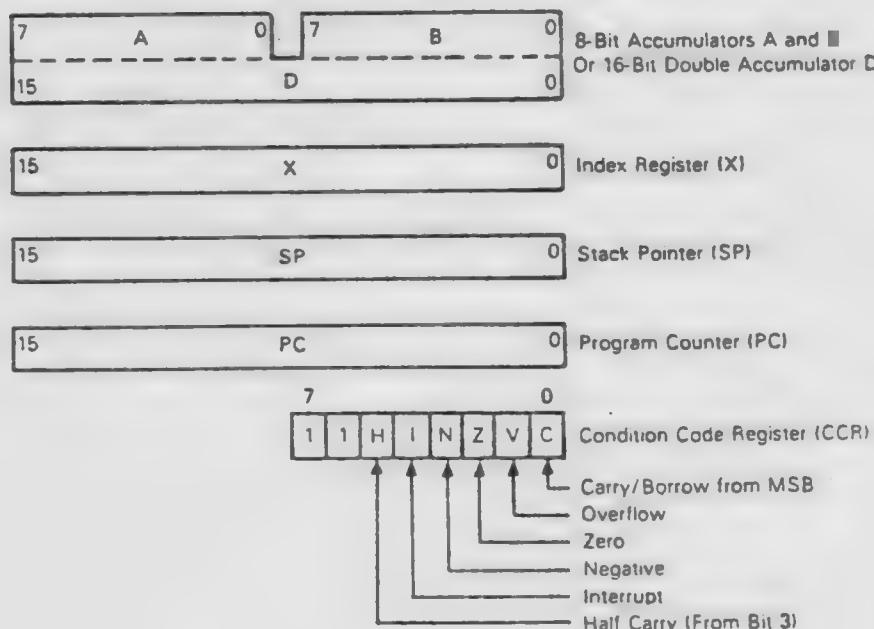

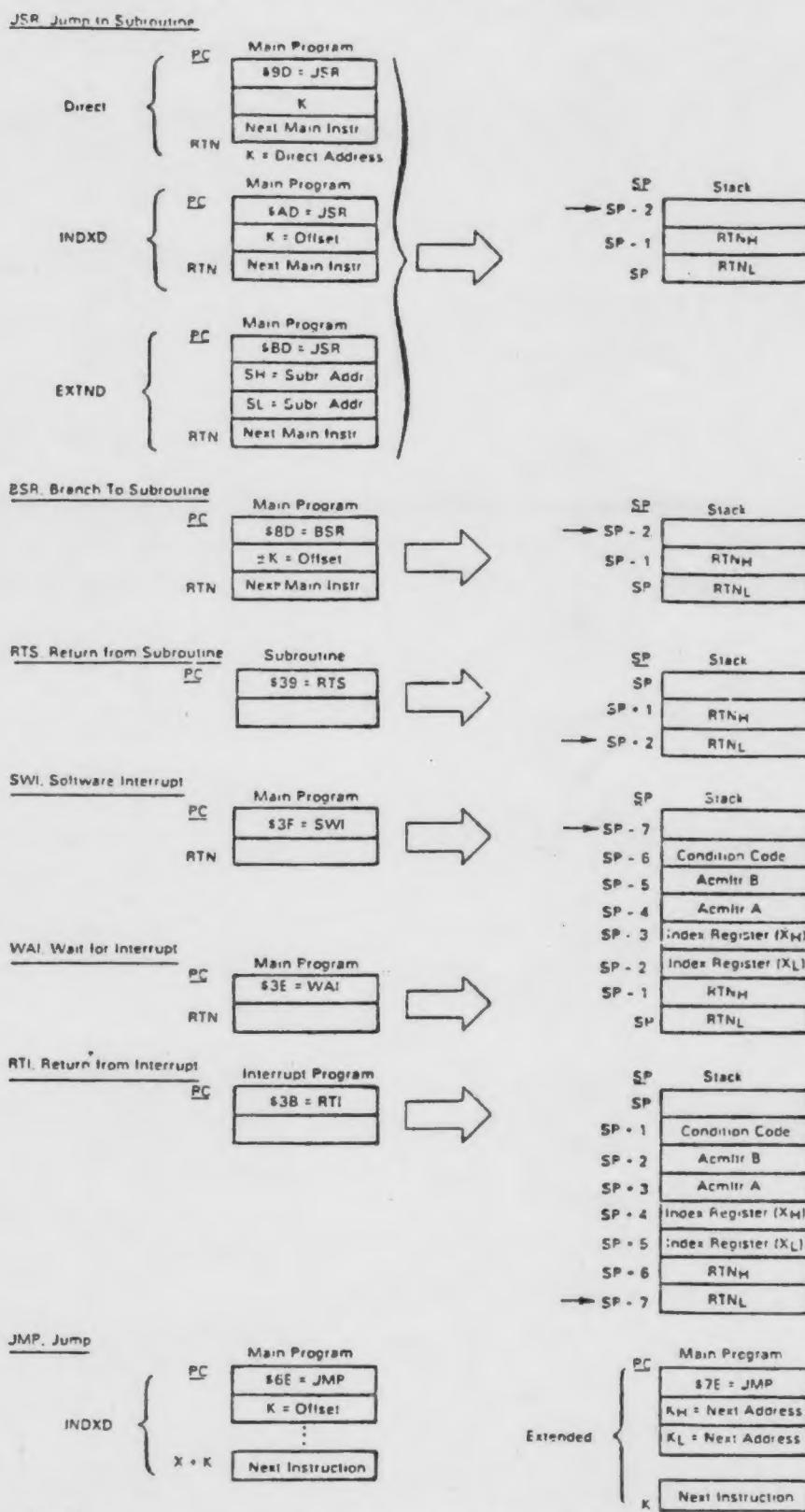

The Microprocessor Unit (MPU) is an enhanced MC6800 MPU with additional capabilities and greater throughput. It is upward source and object code compatible with the MC6800. The programming model is depicted in Figure 11

where Accumulator D is a concatenation of Accumulators A and B. A list of new operations added to the MC6800 instruction set are shown in Table 1.

The basic difference between the MC6801 and the MC68701 is that the MC6801 has an onboard ROM while the MC68701 has an onboard EPROM. The MC68701 is pin and code compatible with the MC6801 and can be used to emulate the MC6801, allowing easy software development using the onboard EPROM. Software developed using the MC68701 can then be masked into the MC6801 ROM.

In order to support the onboard EPROM, the MC68701 differs from the MC6801 as follows:

- (1) Mode 0 in the MC6801 is a test mode only, while in the MC68701 Mode 0 is also used to program the onboard EPROM and has interrupt vectors at \$BFF0-\$BFFF rather than \$FFF0-\$FFFF.

- (2) The MC68701 RAM/EPROM Control Register has two bits used to control the EPROM in Mode 0 that are not defined in the MC6801 RAM Control Register.

- (3) The RESET/V<sub>pp</sub> pin in the MC68701 is dual purpose, used to supply EPROM power as well as to reset the device; while in the MC6801 the pin is called RESET and is used only to reset the device.

In addition, MC6801 modes 1R and 6R, available as a mask option, are not available in the MC68701.

FIGURE 11 — MC68701/6801/6803 PROGRAMMING MODEL

**MOTOROLA Semiconductor Products Inc.**

TABLE 1 — NEW INSTRUCTIONS

| Instruction  | Description                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| ABX          | Unsigned addition of Accumulator B to Index Register                                                                            |

| ADDD         | Adds (without carry) the double accumulator to memory and leaves the sum in the double accumulator                              |

| ASLD or LSLD | Shifts the double accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C-bit              |

| BHS          | Branch if Higher or Same, unsigned conditional branch (same as BCC)                                                             |

| BLO          | Branch if Lower, Unsigned conditional branch (same as BCS)                                                                      |

| BRN          | Branch Never                                                                                                                    |

| JSR          | Additional addressing mode, direct                                                                                              |

| LDD          | Loads double accumulator from memory                                                                                            |

| LSL          | Shifts memory or accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C-bit (same as ASL) |

| LSRD         | Shifts the double accumulator right (towards LSB) one bit; the MSB is cleared and the LSB is shifted into the C-bit             |

| MUL          | Unsigned multiply; multiplies the two accumulators and leaves the product in the double accumulator                             |

| PSHX         | Pushes the Index Register to stack                                                                                              |

| PULX         | Pulls the Index Register from stack                                                                                             |

| STD          | Stores the double accumulator to memory                                                                                         |

| SUBD         | Subtracts memory from the double accumulator and leaves the difference in the double accumulator                                |

| CPX          | Internal processing modified to permit its use with any conditional branch instruction                                          |

## OPERATING MODES

The MCU provides eight different operating modes which are selectable by hardware programming and referred to as Mode 0 through Mode 7. The operating mode controls the memory map, configuration of Port 3, Port 4, SC1, SC2, and the physical location of interrupt vectors.

### FUNDAMENTAL MODES

The MCU's eight modes can be grouped into three fundamental modes which refer to the type of bus it supports: Single Chip, Expanded Non-Multiplexed, and Expanded Multiplexed. Modes 4 and 7 are Single Chip Modes. Mode 5 is the Expanded Non-Multiplexed Mode, and the remaining modes are Expanded Multiplexed Modes. Table 2 summarizes the characteristics of the operating modes.

#### Single Chip Modes (4, 7)

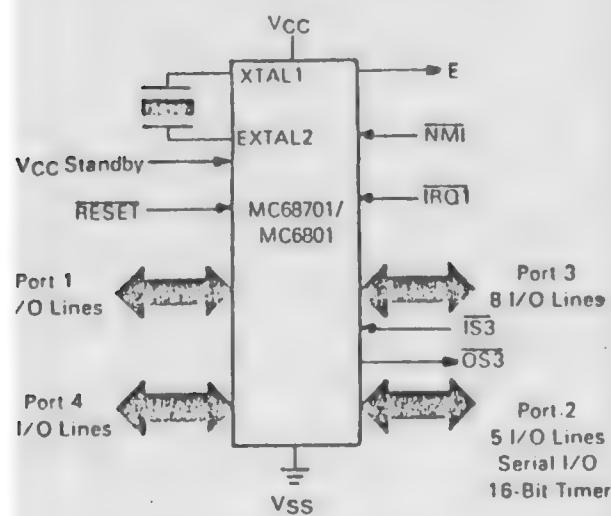

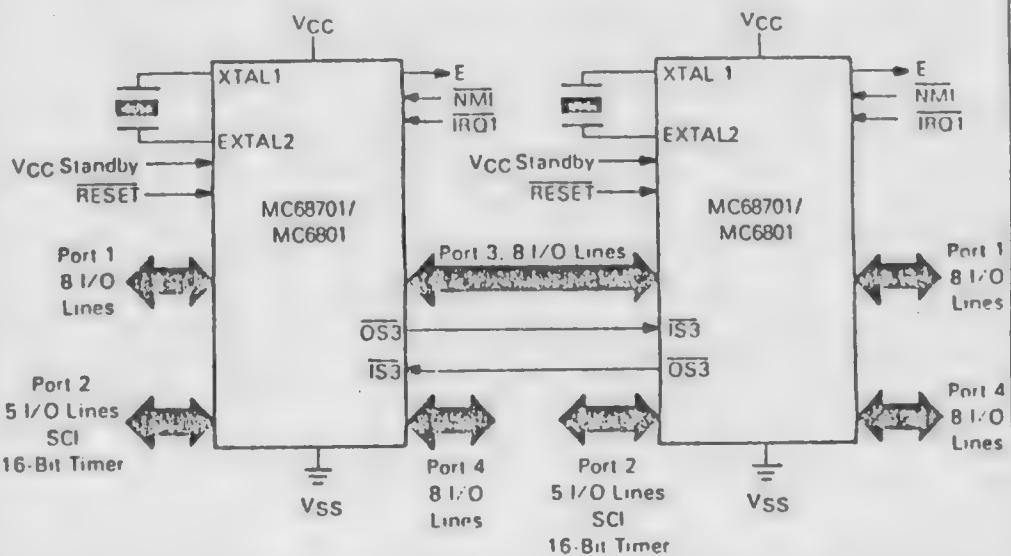

In Single-Chip Mode, the MCU's four ports are configured as parallel input/output data ports, as shown in Figure 12. The MCU functions as a monolithic microcomputer in these two modes without external address or data buses. A maximum of 29 I/O lines and two Port 3 control lines are provided. In addition to other peripherals, another MCU can be interfaced to Port 3 in a loosely coupled dual processor configuration, as shown in Figure 13.

In Single-Chip Test Mode (4), the RAM responds to \$XX20 through \$XXFF and the EPROM is removed from the internal address map. A test program must first be loaded into the RAM using modes 0, 1, 2, or 6. If the MCU is Reset and then programmed into Mode 4, execution will begin at \$XXFE:XXFF. Mode 5 can be irreversibly entered from Mode 4 without going through Reset by setting bit 5 of Port 2's Data Register. This mode is used primarily to test Ports 3 and 4 in the Single-Chip and Non-Multiplexed Modes.

TABLE 2 — SUMMARY OF MC68701 OPERATING MODES

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Common to all Modes:                  | Reserved Register Area<br>Port 1<br>Port 2<br>Programmable Timer<br>Serial Communications Interface                                                                                                                                                                                                                                                                                             |

| Single Chip Mode 7                    | 128 bytes of RAM; 2048 bytes of EPROM<br>Port 3 is a parallel I/O port with two control lines<br>Port 4 is a parallel I/O port<br>SC1 is Input Strobe 3 (IS3)<br>SC2 is Output Strobe 3 (OS3)                                                                                                                                                                                                   |

| Expanded Non-Multiplexed Mode 5       | 128 bytes of RAM; 2048 bytes of EPROM<br>256 bytes of external memory space<br>Port 3 is an 8-bit data bus<br>Port 4 is an input port/address bus<br>SC1 is Input/Output Select (IOS)<br>SC2 is Read/Write (R/W)                                                                                                                                                                                |

| Expanded Multiplexed Modes 1, 2, 3, 6 | Four memory space options (64K address space):<br>(1) No internal RAM or EPROM (Mode 3)<br>(2) Internal RAM, no EPROM (Mode 2)<br>(3) Internal RAM and EPROM (Mode 1)<br>(4) Internal RAM, EPROM with partial address bus (Mode 6)<br>Port 3 is a multiplexed address/data bus<br>Port 4 is an address bus (inputs/address in Mode 6)<br>SC1 is Address Strobe (AS1)<br>SC2 is Read/Write (R/W) |

| Test Mode 4                           | (1) May be changed to Mode 5 without going through Reset<br>(2) May be used to test Ports 3 and 4 as I/O ports                                                                                                                                                                                                                                                                                  |

| Expanded Multiplexed Mode 0           | (1) Internal RAM and EPROM<br>(2) External interrupt vectors located at \$BFF0-\$BFFF<br>(3) Used to program EPROM                                                                                                                                                                                                                                                                              |

**MOTOROLA** Semiconductor Products Inc.

FIGURE 12 – SINGLE CHIP MODE

FIGURE 13 – SINGLE CHIP DUAL PROCESSOR CONFIGURATION

FIGURE 14 – EXPANDED NON-MULTIPLEXED CONFIGURATION

E: pag 15 e 5 e 3

## MC68000 MODES

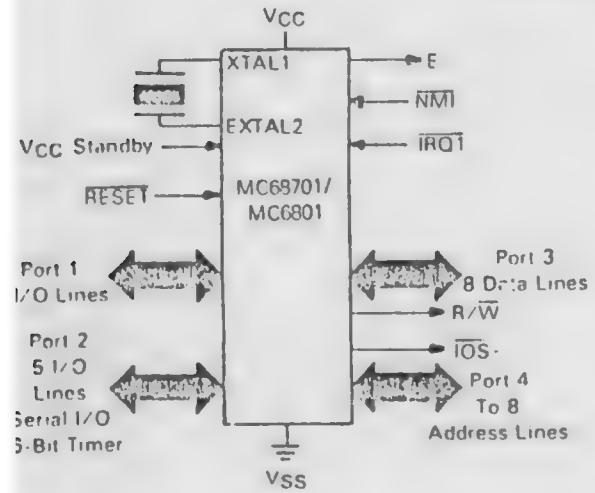

### Expanded Non-Multiplexed Mode (5)

A modest amount of external memory space is provided in the Expanded Non-Multiplexed Mode while retaining significant on-chip resources. Port 3 functions as an 8-bit bidirectional data bus and Port 4 is configured as an input data port. Any combination of the eight least-significant address lines may be obtained by writing to Port 4's Data Direction Register. Stated alternatively, any combination of A0 to A7 may be provided while retaining the remainder as input data lines. Internal pullup resistors are intended to pull Port 4's lines high until it is configured.

Figure 14 illustrates a typical system configuration in the Expanded Non-Multiplexed Mode. The MCU interfaces directly with M6800 family parts and can access 256 bytes of external address space at \$100 through \$1FF.  $\overline{IOS}$  provides an address decode of external memory (\$100-\$1FF) and can be used similarly to an address or chip select line.

### Expanded-Multiplexed Modes (0, 1, 2, 3, 6)

In the Expanded-Multiplexed Modes, the MCU has the ability to access a 64K byte memory space. Port 3 functions as a time multiplexed address/data bus with address valid on the negative edge of Address Strobe (AS) and the data bus valid while E is high. In Modes 0 to 3, Port 4 provides address lines A8 to A15. In Mode 6, however, Port 4 is configured during RESET as data port inputs and the Data Direction Register can be changed to provide any combination of address lines, A8 to A15. Stated alternatively, any subset of A8 to A15 can be provided while retaining the remainder as input data lines. Internal pullup resistors are intended to pull Port 4's lines high until software configures the port.

Figure 15 depicts a typical configuration for the Expanded-Multiplexed Modes. Address Strobe can be used to control a transparent D-type latch to capture addresses A0 to A7, as shown in Figure 16. This allows Port 3 to function as a Data Bus when E is high.

In Mode 0, the internal and external data buses are connected; there must therefore be no memory map overlap in order to avoid potential bus conflicts. Mode 0 is used to program the on board EPROM. All interrupt vectors are external in this mode and are located at \$BFF0-\$BFFF.

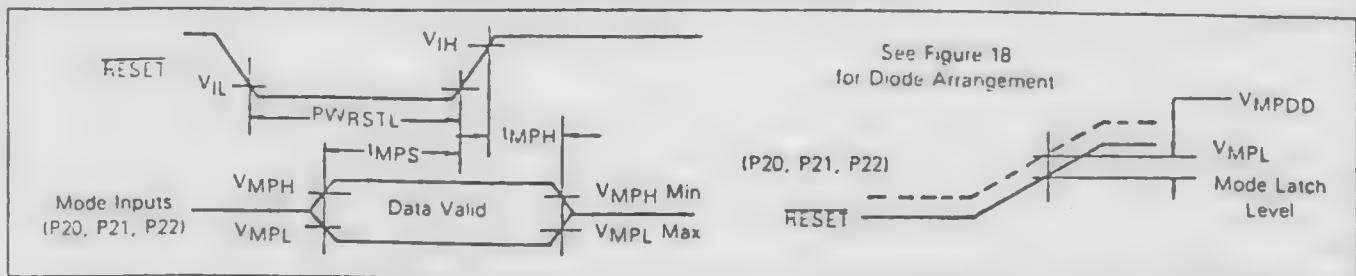

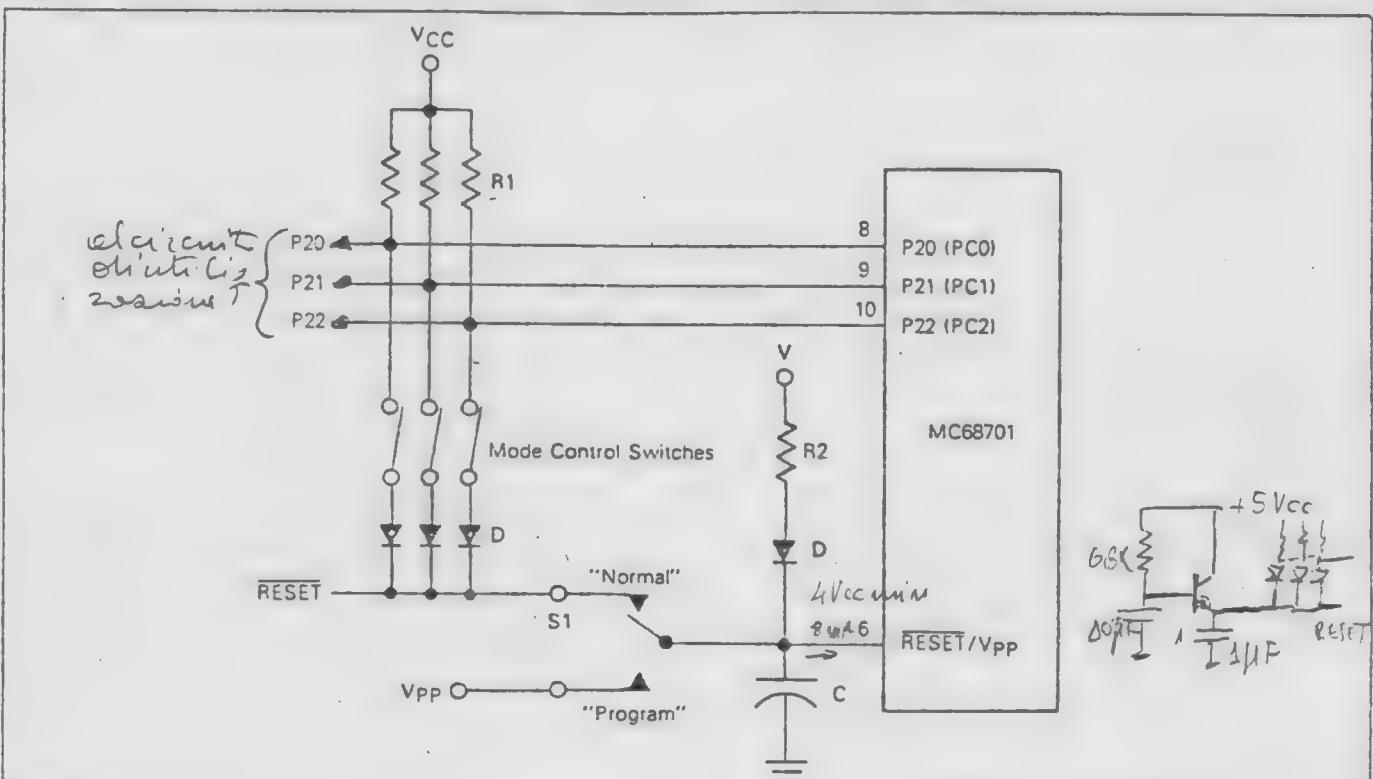

### PROGRAMMING THE MODE

The operating mode is programmed by the levels asserted on P22, P21, and P20 which are latched into PC2, PC1, and PC0 of the program control register on the positive edge of RESET. The operating mode may be read from Port 2's Data Register as shown below, and programming levels and timing must be met as shown in Figure 17. A brief outline of the operating modes is shown in Table 3.

### PART 2 DATA REGISTER

Circuitry to provide the programming levels is dependent primarily on the normal system usage of the three pins. If configured as outputs, the circuit shown in Figure 18 may be used; otherwise, three-state buffers can be used to provide isolation while programming the mode.

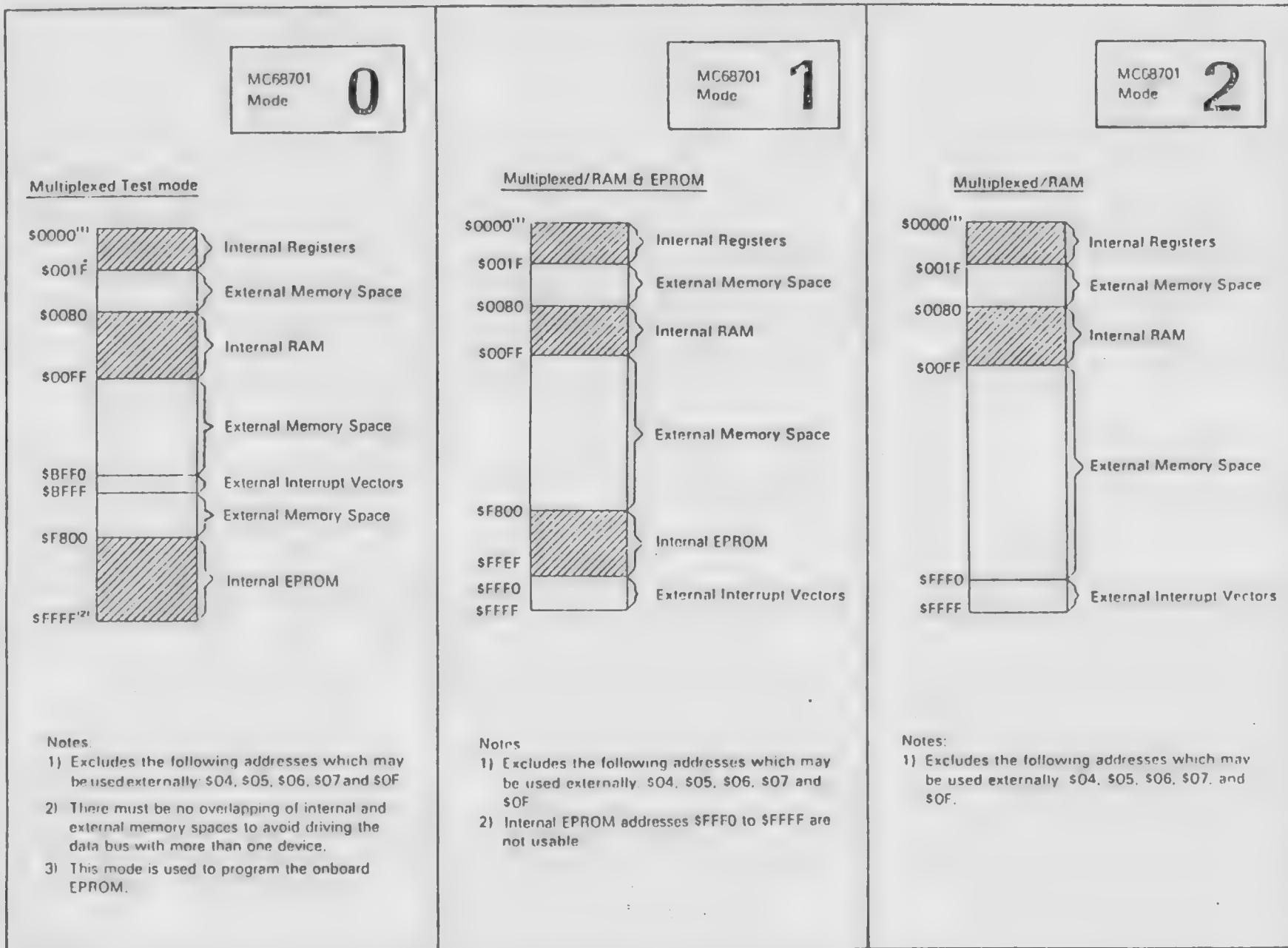

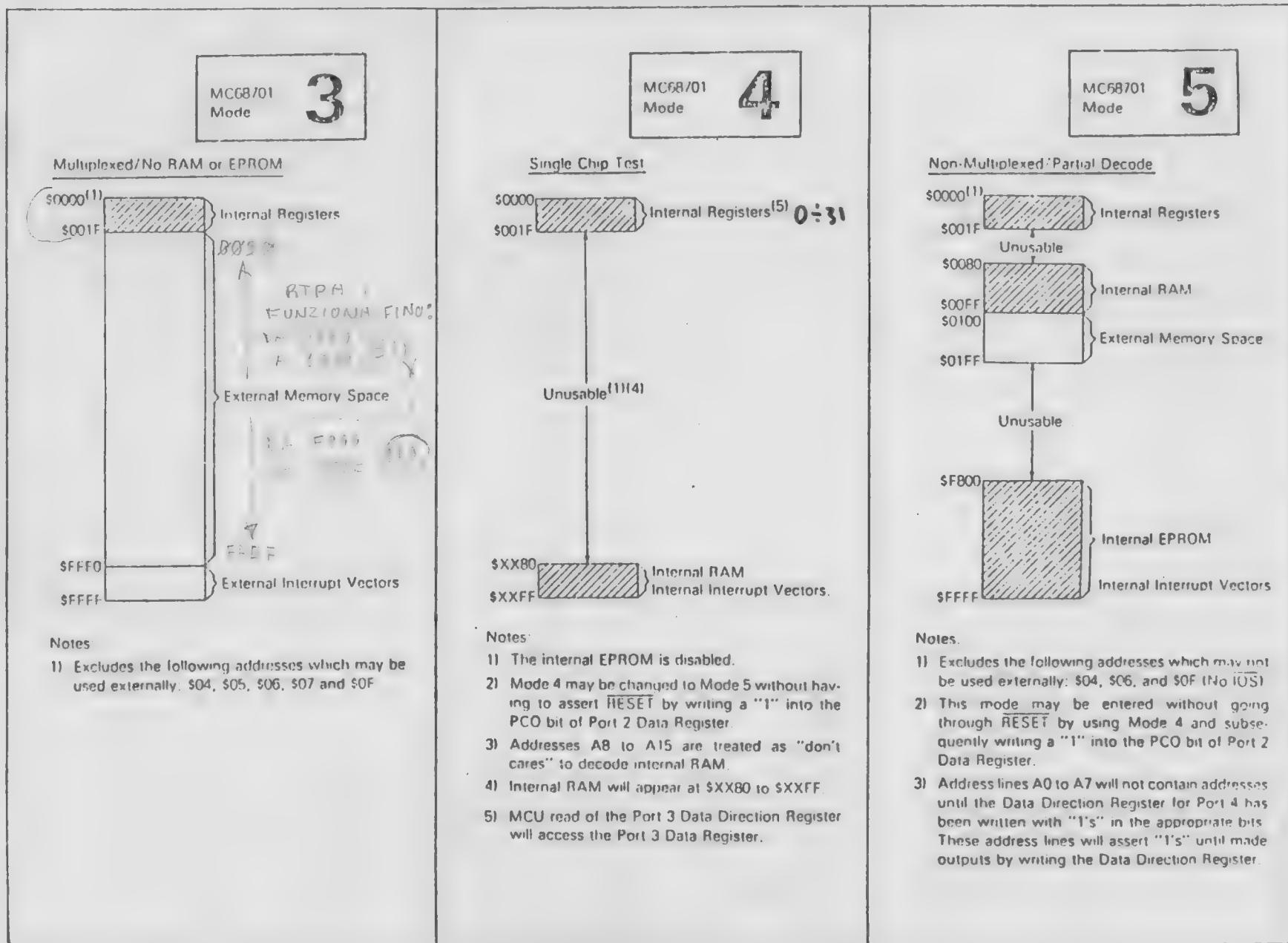

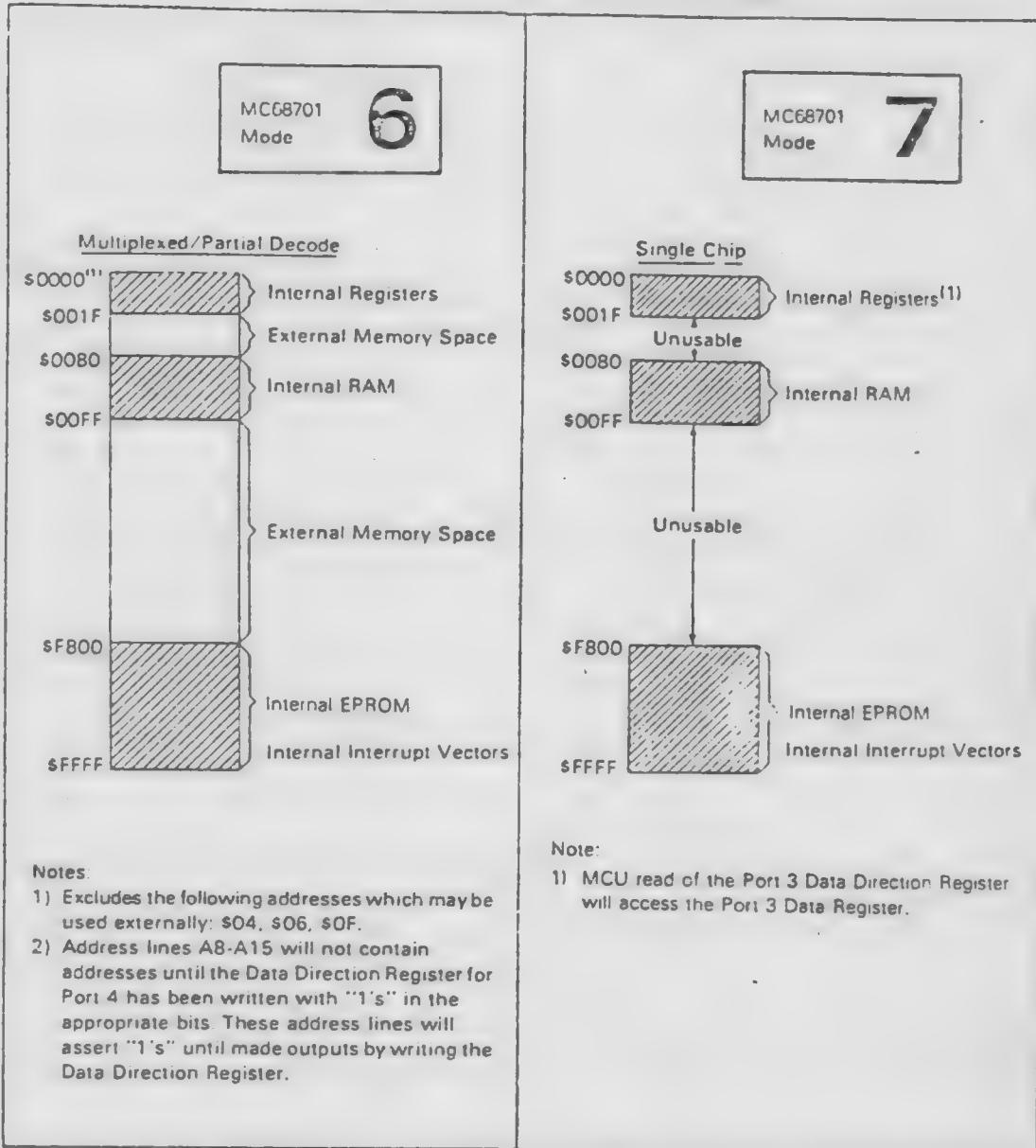

### MEMORY MAPS

The MCU can provide up to 64K byte address space depending on the operating mode. A memory map for each operating mode is shown in Figure 19. The first 32 locations of each map are reserved for the MCU's internal register area, as shown in Table 4, with exceptions as indicated.

TABLE 3 — MODE SELECTION SUMMARY

| Mode | P22<br>PC2 | P21<br>PC1 | P20<br>PC0 | EPROM            | RAM              | Interrupt<br>Vectors | Bus<br>Mode        | Operating<br>Mode              |

|------|------------|------------|------------|------------------|------------------|----------------------|--------------------|--------------------------------|

| 7    | H          | H          | H          | I                | I                | I                    | I                  | Single Chip                    |

| 6    | H          | H          | L          | I                | I                | I                    | MUX(5, 6)          | Multiplexed/Partial Decode     |

| 5    | H          | L          | H          | I                | I                | I                    | NMUX(5, 6)         | Non-Multiplexed/Partial Decode |

| 4    | H          | L          | L          | I <sup>(2)</sup> | I <sup>(1)</sup> | I                    | I                  | Single Chip Test               |

| 3    | L          | H          | H          | E                | E                | E                    | MUX <sup>(4)</sup> | Multiplexed/No RAM or ROM      |

| 2    | L          | H          | L          | E                | I                | E                    | MUX <sup>(4)</sup> | Multiplexed/RAM                |

| 1    | L          | L          | H          | I                | I                | E                    | MUX <sup>(4)</sup> | Multiplexed/RAM & ROM          |

| 0    | L          | L          | L          | I                | I                | K <sup>(3)</sup>     | MUX <sup>(4)</sup> | Multiplexed/Programming        |

#### Legend

- I — Internal

- E — External

- MUX — Multiplexed

- NMUX — Non-Multiplexed

- L — Logic '0'

- H — Logic '1'

#### Notes

- (1) Internal RAM is addressed at \$XX80

- (2) Internal EPROM is disabled

- (3) Interrupt vectors located at \$BFF0-\$BFFF

- (4) Addresses associated with Ports 3 and 4 are considered external in Modes 0, 1, 2, and 3

- (5) Addresses associated with Port 3 are considered external in Modes 5 and 6

MC68701/MC68701-5

FIGURE 15 – EXPANDED MULTIPLEXED CONFIGURATION

FIGURE 16 – TYPICAL LATCH ARRANGEMENT

FIGURE 17 — MODE PROGRAMMING TIMING

## MODE PROGRAMMING (Refer to Figure 17)

| Characteristic                                           | Symbol | Min | Typ | Max | Unit     |

|----------------------------------------------------------|--------|-----|-----|-----|----------|

| Mode Programming Input Voltage Low                       | VMPL   | —   | —   | 1.8 | Vdc      |

| Mode Programming Input Voltage High                      | VMPH   | 4.0 | —   | —   | Vdc      |

| Mode Programming Diode Differential (If Diodes are Used) | VMPPD  | 0.6 | —   | —   | Vdc      |

| RESET Low Pulse Width                                    | PWRSTL | 3.0 | —   | —   | E-Cycles |

| Mode Programming Set-Up Time                             | IMPS   | 2.0 | —   | —   | E-Cycles |

| Mode Programming Hold Time                               | IMPH   | 0   | —   | —   | ns       |

| RESET Rise Time $\geq 1 \mu s$                           |        | 100 | —   | —   |          |

| RESET Rise Time $< 1 \mu s$                              |        | —   | —   | —   |          |

FIGURE 18 — TYPICAL MODE PROGRAMMING CIRCUIT

## Notes:

1. Mode 0 as shown.

2.  $R1 = 10 \text{ kohms (typical)}$ .

3. The RESET time constant is equal to  $RC$  where  $R$  is the equivalent parallel resistance of  $R2$  and the number of resistors ( $R1$ ) placed in the circuit by closed mode control switches.

4.  $D = 1N914, 1N4001$  (typical).

5. If  $V = V_{CC}$ , then  $R2 = 50 \text{ ohms (typical)}$  to meet  $V_{IH}$  for the RESET/VPP pin.  $V = V_{CC}$  is also compatible with MC6801. The RESET time constant in this case is approximately  $R2 \cdot C$ .

6. Switch S1 allows selection of normal (RESET) or programming (VPP) as the input to the RESET/VPP pin. During switching, the input level is held at a value determined by a diode (D), resistor (R2) and input voltage (V).

7. While S1 is in the "Program" position, RESET should not be asserted.

8. From powerup, RESET must be held low for at least  $1\mu\text{sec}$ . The capacitor, C, is shown for conceptual purposes only and is on the order of  $1000 \mu\text{F}$  for the circuit shown. Typically, a driver with an RC input will be used to drive RESET, eliminating the need for the larger capacitor.

MOTOROLA Semiconductor Products Inc.

FIGURE 19 – MC68701 MEMORY MAPS

FIGURE 19 – MC68701 MEMORY MAPS (CONTINUED)

FIGURE 19 — MC68701 MEMORY MAPS (CONCLUDED)

TABLE 4 — INTERNAL REGISTER AREA

| Register                            | Address | Register                                     | Address |

|-------------------------------------|---------|----------------------------------------------|---------|

| Port 1 Data Direction Register***   | 00      | Output Compare Register (Low Byte)           | 0C      |

| Port 2 Data Direction Register***   | 01      | Input Capture Register (High Byte)           | 0D      |

| Port 1 Data Register                | 02      | Input Capture Register (Low Byte)            | 0E      |

| Port 2 Data Register                | 03      | Port 3 Control and Status Register           | 0F*     |

| Port 3 Data Direction Register***   | 04*     | Rate and Mode Control Register               | 10      |

| Port 4 Data Direction Register***   | 05**    | Transmit/Receive Control and Status Register | 11      |

| Port 3 Data Register                | 06*     | Receive Data Register                        | 12      |

| Port 4 Data Register                | 07**    | Transmit Data Register                       | 13      |

| Timer Control and Status Register   | 08      | RAM Control Register                         | 14      |

| Counter (High Byte)                 | 09      | Reserved                                     | 15-1F   |

| Counter (Low Byte)                  | 0A      |                                              |         |

| Output Compare Register (High Byte) | 0B      |                                              |         |

\*External addresses in Modes 0, 1, 2, 3, 5, 6, cannot be accessed in Mode 5 (No  $\overline{IOS}$ )

\*\*External addresses in Modes 0, 1, 2, 3

\*\*\*1 = Output, 0 = Input

MOTOROLA Semiconductor Products Inc.

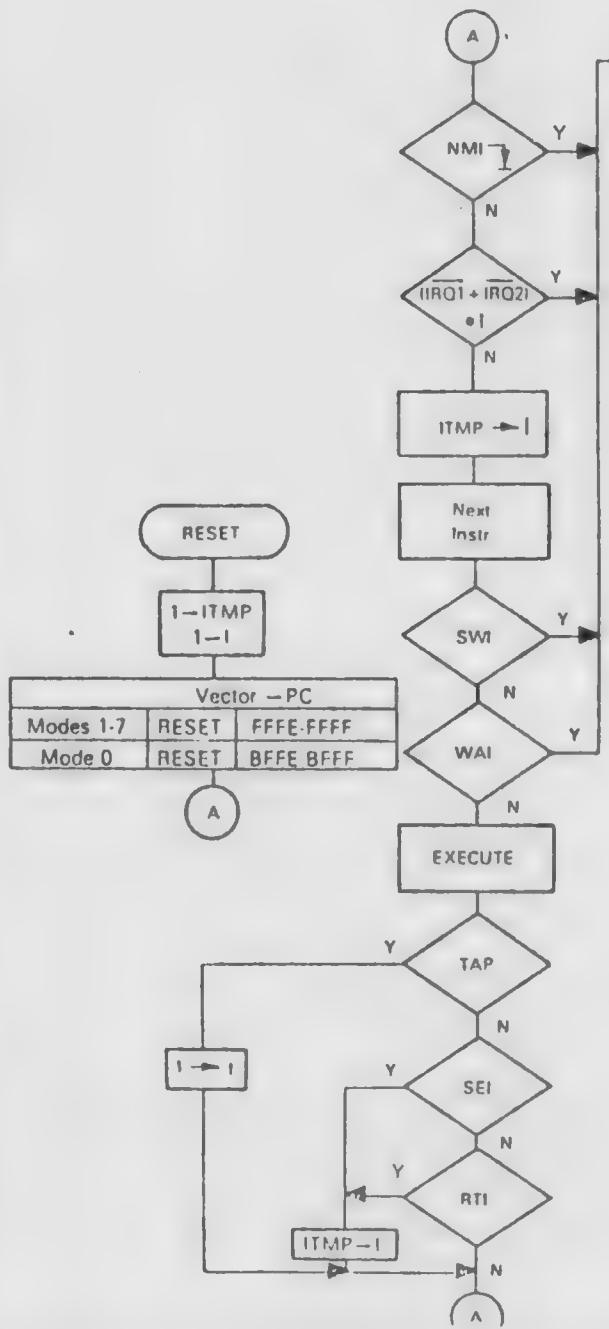

## MC68701 INTERRUPTS

The MCU supports two types of interrupt requests: maskable and non-maskable. A Non-Maskable Interrupt (NMI) is always recognized and acted upon at the completion of the current instruction. Maskable interrupts are controlled by the Condition Code Register's I-bit and by individual enable bits. The I-bit controls all maskable interrupts. Of the maskable interrupts, there are two types: IRQ1 and IRQ2. The Programmable Timer and Serial Communications Interface use an internal IRQ2 interrupt line, as shown in Figure 1. External devices (and TS3) use IRQ1. An IRQ1 interrupt is serviced before IRQ2 if both are pending.

All IRQ2 interrupts use hardware prioritized vectors. The single SCI interrupt and three timer interrupts are serviced in a prioritized order where each is vectored to a separate location. All MCU interrupt vector locations are shown in Table 5.

TABLE 5 – MCU INTERRUPT VECTOR LOCATIONS

| Mode 0 |      | Modes 1-7 |      | Interrupt                |

|--------|------|-----------|------|--------------------------|

| MSB    | LSB  | MSB       | LSB  |                          |

| BFFE   | BFFF | FFFE      | FFFF | RESET                    |

| BFFC   | BFFD | FFFC      | FFFD | NMI                      |

| BFFA   | BFFB | FFFA      | FFFB | Software Interrupt (SWI) |

| BFF8   | BFF9 | FFFB      | FFF9 | IRQ1 (or TS3)            |

| BFF6   | BFF7 | FFF6      | FFF7 | ICF (Input Capture)      |

| BFF4   | BFF5 | FFF4      | FFF5 | OCF (Output Compare)     |

| BFF2   | BFF3 | FFF2      | FFF3 | TOF (Timer Overflow)     |

| BFFC   | BFF1 | FFFO      | FFF1 | SCI (RDRE + ORFE + TDRE) |

The Interrupt flowchart is depicted in Figure 20 and is common to every MCU interrupt excluding Reset. The Program Counter, Index Register, A Accumulator, B Accumulator, and Condition Code Register are pushed to the stack. The I-bit is set to inhibit maskable interrupts and a vector is fetched corresponding to the current highest priority interrupt. The vector is transferred to the Program Counter and instruction execution is resumed. Interrupt and RESET timing are illustrated in Figures 21a and 21b.

## FUNCTIONAL PIN DESCRIPTIONS

### VCC AND VSS

VCC and VSS provide power to a large portion of the MCU. The power supply should provide +5 volts ( $\pm 5\%$ ) to VCC, and VSS should be tied to ground. Total power dissipation (including VCC Standby), will not exceed PD milliwatts.

### VCC STANDBY

VCC Standby provides power to the standby portion (\$80 through \$BF) of the RAM and the STBY PWR and RAME bits of the RAM Control Register. Voltage requirements depend on whether the MCU is in a powerup or powerdown state. In the powerup state, the power supply should provide +5 volts ( $\pm 5\%$ ) and must reach VSB volts before RESET reaches 4.0 volts. During powerdown, VCC Standby must remain above VSBB (min) to sustain the standby RAM and STBY PWR bit. While in powerdown operation, the standby current will not exceed ISBB.

It is typical to power both VCC and VCC Standby from the same source during normal operation. A diode must be used between them to prevent supplying power to VCC during powerdown operation. VCC Standby should be tied to either ground or VCC in Mode 3.

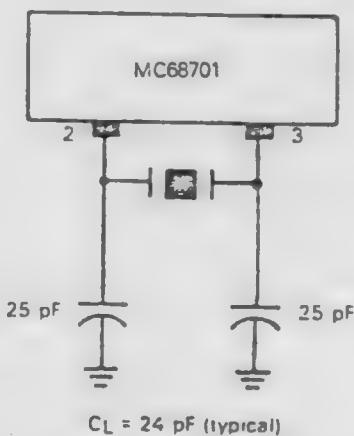

### XTAL1 AND XTAL2

These two input pins interface either a crystal or TTL compatible clock to the MCU's internal clock generator. Divide-by-four circuitry is included which allows use of the inexpensive 3.58 MHz or 4.4336 MHz Color Burst TV crystals. A 25 pF capacitor is required from each crystal pin to ground to ensure reliable startup and operation. Alternatively, EXTAL2 may be driven with an external TTL compatible clock at 4f<sub>0</sub> with a duty cycle of 50% ( $\pm 10\%$ ) with XTAL1 connected to ground.

The internal oscillator is designed to interface with an AT-cut quartz crystal resonator operated in parallel resonance mode in the frequency range specified for XTAL. The crystal should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time. The MCU is compatible with most commercially available crystals, and nominal crystal parameters are shown in Figure 22.

### RESET/VPP